User’s Manual U16898EJ3V0UD

387

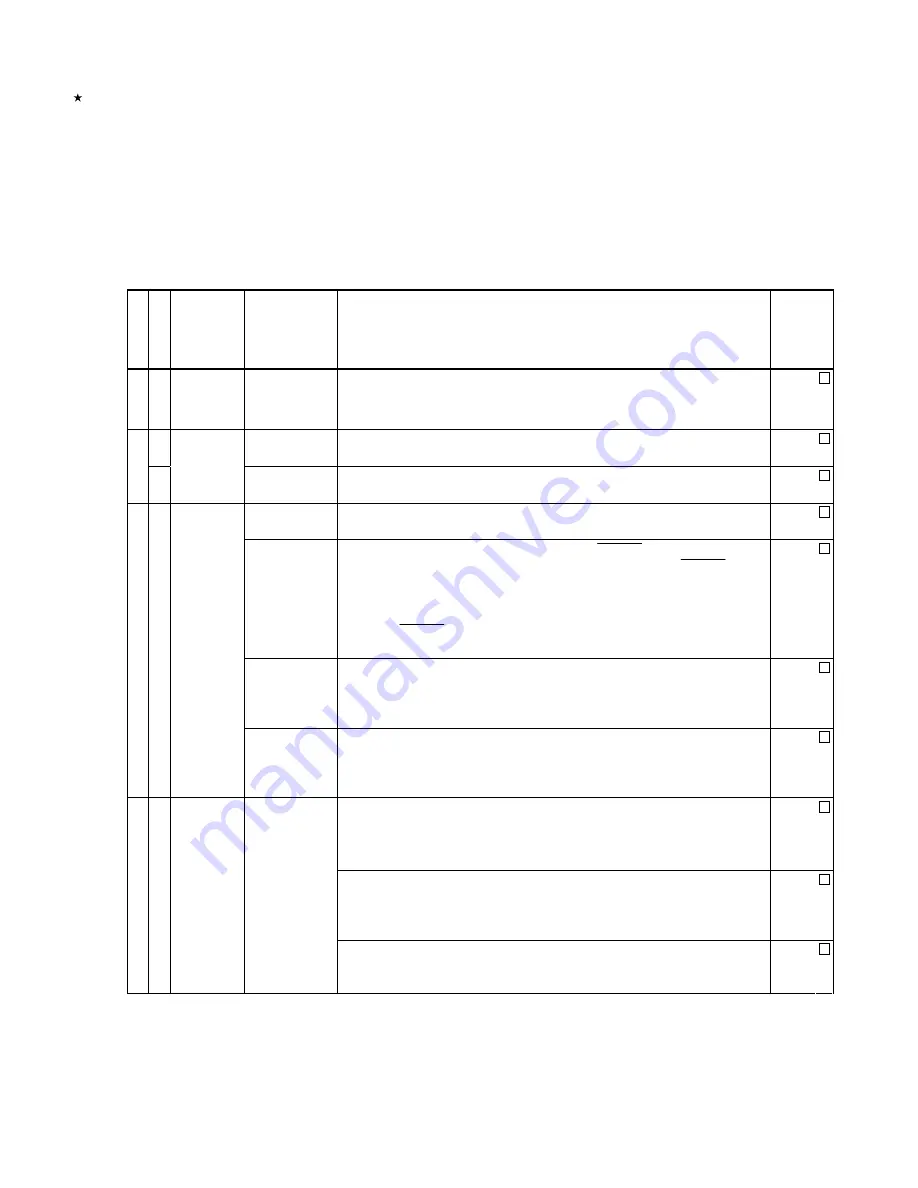

APPENDIX D LIST OF CAUTIONS

This appendix lists cautions described in this document.

“Classification (hard/soft)” in table is as follows.

Hard: Cautions for microcontroller internal/external hardware

Soft: Cautions for software such as register settings or programs

(1/17)

Chapter

Classification

Function Details

of

Function

Cautions Page

pp. 21,

Chapter 2

Hard

Pin

functions

P121/X1,

P122/X2

The P121/X1 and P122/X2 pins are pulled down during reset.

22, 24, 25

Hard

Vector table

address

No interrupt sources correspond to the vector table address 0014H.

p. 29

Chapter 3

Soft

Memory

space

SP: stack

pointer

Since reset signal generation makes the SP contents undefined, be sure to

initialize the SP before using the stack memory.

p. 33

P121/X1,

P122/X2

The P121/X1 and P122/X2 pins are pulled down during reset.

p. 49

P34

Because the P34 pin functions alternately as the RESET pin, if it is used as an

input port pin, the function to input an external reset signal to the RESET pin

cannot be used. The function of the port is selected by the option byte. For

details, refer to CHAPTER 17 OPTION BYTE.

Also, since the option byte is referenced after the reset release, if low level is

input to the RESET pin before the referencing, then the reset state is not

released. When it is used as an input port pin, connect the pull-up resistor.

p. 53

P31, P31, P43 Because P30, P31, and P43 are also used as external interrupt pins, the

corresponding interrupt request flag is set if each of these pins is set to the

output mode and its output level is changed. To use the port pin in the output

mode, therefore, set the corresponding interrupt mask flag to 1 in advance.

p. 60

Chapter 4

Hard

Port

functions

−

Although a 1-bit memory manipulation instruction manipulates 1 bit, it accesses

a port in 8-bit units. Therefore, the contents of the output latch of a pin in the

input mode, even if it is not subject to manipulation by the instruction, are

undefined in a port with a mixture of inputs and outputs.

p. 65

To set and then release the STOP mode, set the oscillation stabilization time as

follows.

Expected oscillation stabilization time of resonator

≤

Oscillation stabilization

time set by OSTS

p. 71

The wait time after the STOP mode is released does not include the time from

the release of the STOP mode to the start of clock oscillation (“a” in the figure

below), regardless of whether STOP mode was released by reset input or

interrupt generation.

p. 71

Chapter 5

Soft

Main clock

OSTS:

Oscillation

stabilization

time select

register

The oscillation stabilization time that elapses on power application or after

release of reset is selected by the option byte. For details, refer to CHAPTER

17 OPTION BYTE.

p. 71