GR716-DS-UM, May 2019, Version 1.29

273

www.cobham.com/gaisler

GR716

29.6.15

Table 327.

0x100+n*0x20 - SEQCTRL0 - Sequence control register 0

Sequence Control Register 0

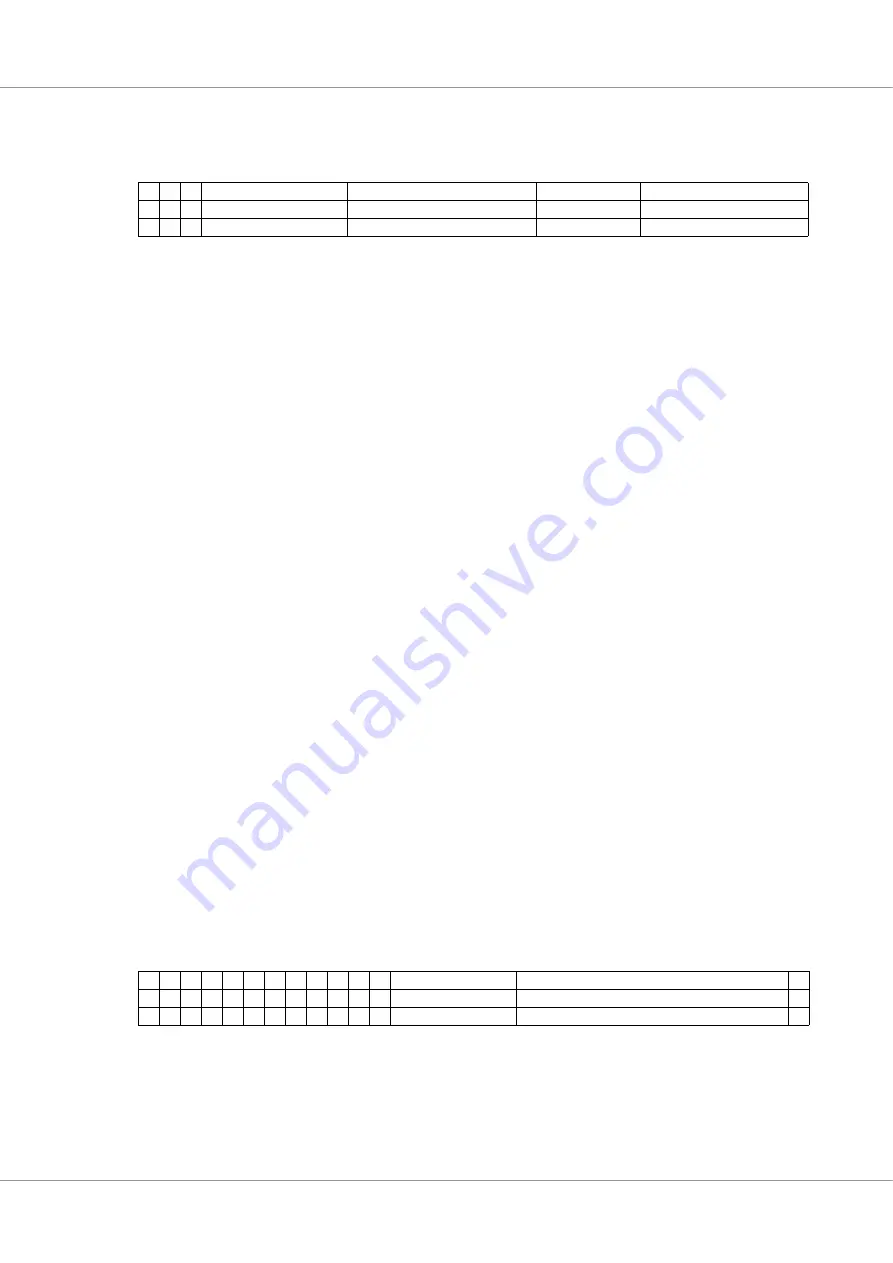

29.6.16 Sequence Control Register 1

31 30 29 28

21 20

13 12

8

7

0

SQ SI SE

SDEL

SEQCNT

SEQLEN

SEQDIV

0

0

0

0x00

0x00

0x00

0x00

rw rw rw

rw

rw

rw

rw

31

SQ: Sequence synchronization enable. If set to 1, the output sequence from GPIO output pin n will

be synchronized to synchronization source selected in register SEQSYNC. If set to 0, SEQDIV will

be used to generate internally the sequence rate. The latter case is not supported in cascade mode,

and this bit must be set to 1 in all the GPIOs in the cascade.

30

SI: Sequence Interrupt enable. By enable this bit an interrupt will be generated when the sequence is

complete

29

SE: Sequence enable. When this bit is set, the sequence will be enabled and the sequencer (if

CMODE=0 or CSTART=1) will be granted access to the physical pin. This bit will self-clear when

sequence is complete. If SQ is set to 1 a final trigger event is necessary to set this bit to 0, discon-

necting the GPIO sequencer from the physical pin. In case of SEQLEN is set to continuously output

the sequence the software needs to disable the sequence. When manual termination of the current

sequence will always finish. This field must be set to 1 in all the sequencers in a cascade. When

sequence is enabled, SEQDATA(0) or SEQDATA(31) (depending on REV field) will be outputted.

After this operation, if SQ is set to 0 the count of the delay and data rate will start autonomously. If

SQ is set to 1, the sequencer will wait for an initial triggering event to start counting events, provid-

ing margin for an initial delay of the first bit.

28:

21

SDEL: Set the clock cycle delay between each repetition. By setting this register to ’0’ creates con-

tiguous sequences.

20:

13

SEQCNT: Set the number of times to repeat the loop for GPIO output pin n. The sequence will be

looped 1 times i.e. ’0’ means the sequence will be looped once. Setting the register 0xFF

configures the GPIO sequencer to continuously output the sequence until it is disabled.

When in cascade mode, this value in the GPIO marked as START indicates the number of segments

in the cascade outputted. For this reason this field must follow the equation below:

where is the times the entire cascade will be outputted and

the number of GPIO

sequencers in the cascade. When a different value is selected, the sequence will be correctly out-

putted, although writing 1 to the RE field in Sequence Control Register 1 is required for correct ter-

mination. A’0’ in the SEQCNT field will output the entire cascade once (i.e. it is equivalent to

).

12:

8

SEQLEN: Sequence length. The sequence length is defined as 1 by the sequencer logic.

In cascade mode it must be set to the same value in each GPIO sequencer of the cascade.

7:

0

SEQDIV: Sequence divisor determines the sequence-rate for the GPIO port

Table 328.

0x104+n*0x20 - SEQCTRL1 - Sampling Sequence control register

31 30 29 28 27 26 25 24 23 22 21 20 19

14 13

1

0

SE CT TR IR FD R RS CM CS CE RV EI

INT

Reserved

RE

0

0

0

0

0

0

0

0

0

0

0

0

0x00

0

0

rw rw rw rw rw

r

rw rw rw rw rw rw

rw

r

wc

31

SE: Sampling Enable of GPIO input. Sampling will be enabled when this bit field is set to ’1’. Sam-

pling enable bit will be self-cleared when sampling fifo is full.

30

CT: Continuously sampling of GPIO input. This feature will continuously sample at every clock

cycle or when selected trigger event occur. If this feature isn’t selected sampling will stop immedi-

ately when sampling buffer is full.

29

TR: Sample input using external trigger source selected in SEQSYNC

SEQCNT

K

N

CHAIN

1

–

=

K

N

CHAIN

N

CHAIN

1

–