Debug

ARM DDI 0363E

Copyright © 2009 ARM Limited. All rights reserved.

11-24

ID013010

Non-Confidential, Unrestricted Access

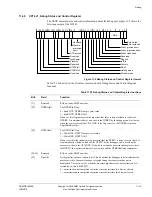

Table 11-17 shows how the bit values correspond with the Breakpoint Control Registers

functions.

Table 11-17 Breakpoint Control Registers functions

Bits

Field

Function

[31:29]

Reserved

Do not modify on writes. On reads, the value returns zero.

[28:24]

Breakpoint

address mask

This field sets a breakpoint on a range of addresses by masking lower order address bits out

of the breakpoint comparison.

a

b00000 = no mask

b00001 = Reserved

b00010 = Reserved

b00011 =

0x00000007

mask for instruction address

b00100 =

0x0000000F

mask for instruction address

b00101 =

0x0000001F

mask for instruction address

...

b11111 =

0x7FFFFFFF

mask for instruction address.

[23]

Reserved

-

[22:20]

M

Meaning of BVR:

b000 = instruction address match

b001 = linked instruction address match

b010 = unlinked context ID

b011 = linked context ID

b100 = instruction address mismatch

b101 = linked instruction address mismatch

b11x = Reserved.

For more information, see Table 11-18 on page 11-25

[19:16]

Linked BRP

number

The binary number encoded here indicates another BRP to link this one with.

Note

•

if a BRP is linked with itself, it is Unpredictable whether a breakpoint debug event is

generated

•

if this BRP is linked to another BRP that is not configured for linked context ID

matching, it is Unpredictable whether a breakpoint debug event is generated.

[15:14]

Secure state

access control

RAZ or SBZP.

[13:9]

Reserved

Do not modify on writes. On reads, the value returns zero.