Introduction

ARM DDI 0363E

Copyright © 2009 ARM Limited. All rights reserved.

1-18

ID013010

Non-Confidential, Unrestricted Access

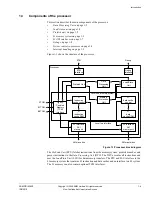

Figure 1-4 Cortex-R4F Issue and Execution pipeline stages

The names of the common pipeline stages and their functions are:

Iss

Register read and instruction issue to execute stages.

Ex

Execute stages.

Wr

Write-back of data from the execution pipelines.

Ret

Instruction retire.

The names of the load/store pipeline stages and their functions are:

DC1

First stage of data memory access.

DC2

Second stage of data memory access.

The names of the floating point pipeline stages and their functions are:

F0

Floating point register read.

F1

First stage of floating point execution.

F2

Second stage of floating point execution.

Fwr

Floating point writeback.

The pipeline structure provides a pipelined 2-cycle memory access and single-cycle load-use

penalty. This enables integration with slow RAM blocks and maintains good CPI at reasonable

frequencies.

Register

read,

address

generation,

and

instruction

issue

EX1

DC1

Exception flush and mispredicted

indirect branches

F0

EX1

DC2

F1

F2

Load/store

pipeline

Data

processing

pipeline

Floating point

pipeline

Iss

Ex1

Ex2

Wr

Ret

Fwr

Mispredicted direct branches

Wr