Introduction

ARM DDI 0363E

Copyright © 2009 ARM Limited. All rights reserved.

1-4

ID013010

Non-Confidential, Unrestricted Access

1.3

Components of the processor

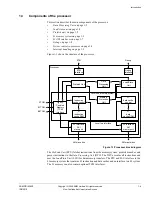

This section describes the main components of the processor:

•

Data Processing Unit

on page 1-5

•

Load/store unit

on page 1-5

•

Prefetch unit

on page 1-5

•

L1 memory system

on page 1-5

•

L2 AXI interfaces

on page 1-7

•

Debug

on page 1-8

•

System control coprocessor

on page 1-9

•

Interrupt handling

on page 1-9.

Figure 1-1 shows the structure of the processor.

Figure 1-1 Processor block diagram

The

PreFetch Unit

(PFU) fetches instructions from the memory system, predicts branches, and

passes instructions to the

Data Processing Unit

(DPU). The DPU executes all instructions and

uses the

Load/Store Unit

(LSU) for data memory transfers. The PFU and LSU interface to the

L1 memory system that contains L1 instruction and data caches and an interface to a L2 system.

The L1 memory can also contain optional TCM interfaces.

Processor

Level two interface

Level one memory system

AXI master bus

AXI slave bus

L2 interface

AXI

master port

Data

Processing

Unit

Memory

Protection

Unit

Prefetch Unit

Load/Store

Unit

L2 interface

AXI

slave port

Tightly-

Coupled

Memory

(TCM)

interface

B0TCM

B1TCM

ATCM

L1

instruction

cache control

L1

instruction

cache RAM

L1

data cache

control

L1

data

cache RAM

Debug

Debug

interface

ETM

ETM

interface