UG-549

ADuCM310 Hardware Reference Manual

Rev. C | Page 20 of 192

0

AV

DD

FS (V

REF

)

–FS (–V

REF

)

AIN+

AIN–

OUTPUT CODE

1

1461-

005

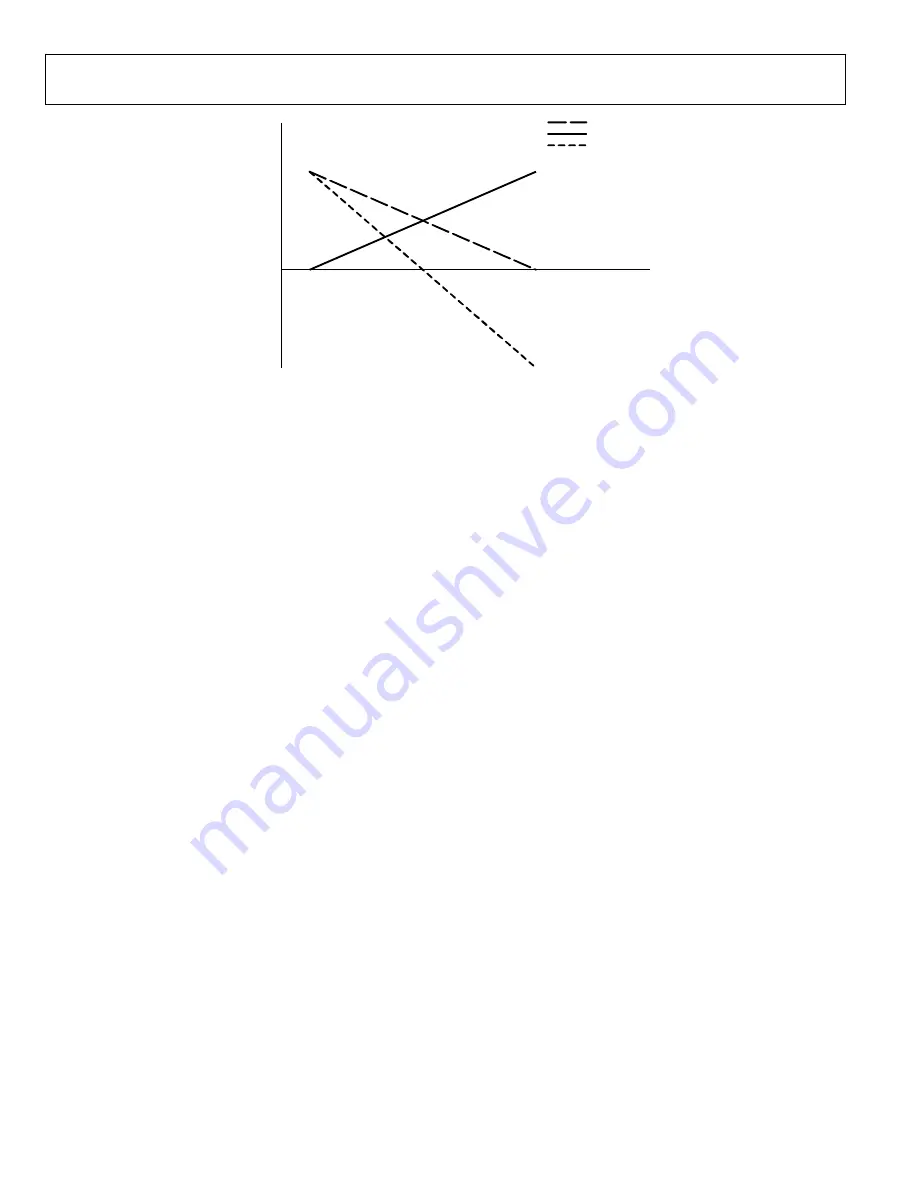

Figure 5. Examples of Balanced Signals for Differential Mode

A high precision, low drift, factory-calibrated 2.505 V reference is provided on-chip. An external reference can also be connected to the

ADC_CAPP and ADC_CAPN pins.

Single or continuous conversion modes can be initiated in software. An external pin (alternate function of P2.4) can also generate a

repetitive trigger for ADC conversions.

ADC CIRCUIT OPERATION

The SAR ADC is based on a charge redistribution DAC. The capacitive DAC consists of two identical arrays of 18 binary weighted

capacitors that are connected to the two inputs of the comparator.

The ADC converts the voltage applied to the positive analog inputs (AIN+) and negative analog inputs (AIN−) in the following three steps:

1.

Precharge Phase: during this phase, the precharge buffers connect the inputs to the capacitor arrays. This charges the capacitors

quickly with minimal loading of the external input source.

2.

Acquisition Phase: during the acquisition phase, the capacitor arrays are connected directly to the inputs to fully charge the capacitor

arrays and eliminate any precharge buffer errors. The timing for the acquisition phase is set by ADCCNVC[25:16]; set this value to

1 µs for ADC update rates ≤500 kSPS (for example, ADCCNVC = 0x140028 for 500 kSPS). If the input buffer is not used when

measuring AV

DD

/2, IOV

DD

/2, or temperature sensor channels, set this value to 1.5 µs.

3.

Conversion Phase: at the end of the acquisition phase, the internal CNV signal goes high and initiates the conversion phase. The

conversion begins with the SW+ and SW− switches being opened. This disconnects the two capacitor arrays from the analog inputs

and connects the analog inputs to AGND (−V

REF

). The conversion is completed by normal successive approximation.

The ADC block operates from an internally generated 20 MHz clock.

The ADC conversion rate is set by ADCCNVC[9:0].

ADC TRANSFER FUNCTION

Single-Ended Mode

In single-ended mode, the input range is 0 to V

REF

. The output coding is straight binary with 1 LSB = FS/65,536 or V

REF

/65,536 =

2.5 V/65,536 = 38.14 µV.

The data values in ADCDATx are aligned such that the MSB is in ADCDATx[27] and, therefore, the LSB is in ADCDATx[12].

The ideal code transitions occur midway between successive integer LSB values (that is, 1/2 LSB, 3/2 LSB, 5/2 LSB, …, FS − 3/2 LSBs). The

ideal input/output transfer characteristic is shown in Figure 6.