UG-549

ADuCM310 Hardware Reference Manual

Rev. C | Page 146 of 192

Bits

Bit Name

Description

Reset

Access

6

HFM

High frequency mode. This bit is used for applications using high frequency

where the pad introduces a significant delay on the SCL, which can cause a

significant enough difference between the serial clock and the data being

received on the Rx shift register. In this mode, the Rx shift register is clocked

by SCL instead of UCLK.

0x0

RW

[5:0]

DIV

SPI clock divider. DIV is the factor that divides HCLK to generate the serial clock.

0x0

RW

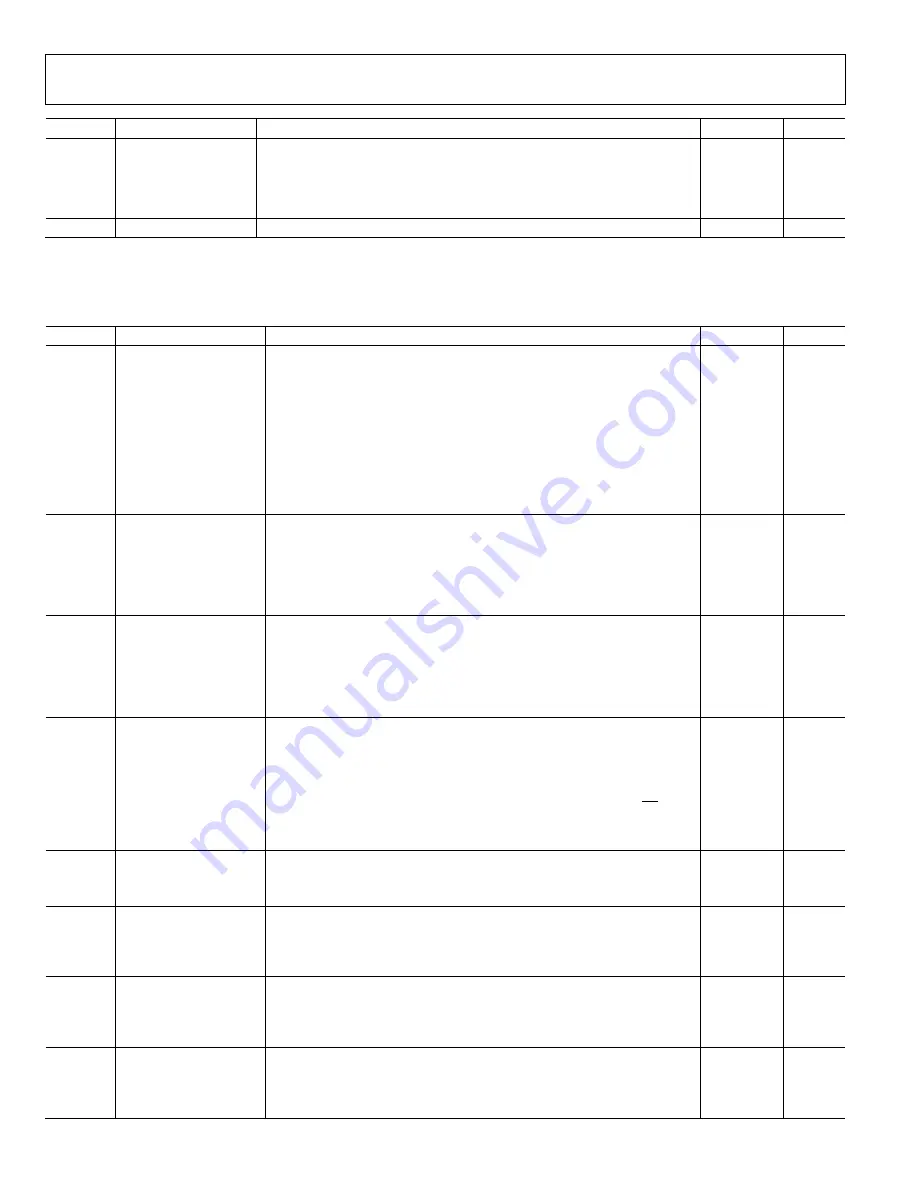

SPI Configuration Register

Address: 0x40030010, Reset: 0x0000, Name: SPI1CON

Table 210. Bit Descriptions for SPI1CON

Bits

Bit Name

Description

Reset

Access

[15:14]

MOD

SPI IRQ mode bits. These bits configure when the Tx/Rx interrupts occur in

a transfer. For DMA Rx transfer, these bits must be 00.

0x0

RW

00: Tx interrupt occurs when 1 byte is transferred. Rx interrupt occurs when

1 or more bytes are received into the FIFO.

01: Tx interrupt occurs when 2 bytes are transferred. Rx interrupt occurs

when 2 or more bytes are received into the FIFO.

10: Tx interrupt occurs when 3 bytes are transferred. Rx interrupt occurs

when 3 or more bytes are received into the FIFO.

11: Tx interrupt occurs when 4 bytes are transferred. Rx interrupt occurs

when the Rx FIFO is full, or 4 bytes present.

13

TFLUSH

SPI Tx FIFO flush enable.

0x0

RW

0: clear this bit to disable Tx FIFO flushing.

1: set this bit to flush the Tx FIFO. This bit does not clear itself and must be

toggled if a single flush is required. If this bit is left high, either the last

transmitted value or 0x00 is transmitted depending on the ZEN bit. Any

writes to the Tx FIFO are ignored while this bit is set.

12

RFLUSH

SPI Rx FIFO flush enable.

0x0

RW

0: clear this bit to disable Rx FIFO flushing.

1: set this bit to flush the Rx FIFO. This bit does not clear itself and must be

toggled if a single flush is required. If this bit is set, all incoming data is

ignored and no interrupts are generated. If set and TIM = 0, a read of the

Rx FIFO initiates a transfer.

11

CON

Continuous transfer enable.

0x0

RW

0: DIS. Cleared by user to disable continuous transfer. Each transfer

consists of a single 8-bit serial transfer. If valid data exists in the SPI1TX

register, a new transfer is initiated after a stall period of 1 serial clock cycle.

1: EN. Set by user to enable continuous transfer. In master mode, the

transfer continues until no valid data is available in the Tx register. CS is

asserted and remains asserted for the duration of each 8-bit serial transfer

until Tx is empty.

10

LOOPBACK

Loopback enable.

0x0

RW

0: cleared by user to be in normal mode.

1: set by user to connect MISO to MOSI and test software.

9

OEN

Slave MISO output enable.

0x0

RW

0: clear this bit to disable the output driver on the MISO pin. The MISO pin

is open-circuit when this bit is clear.

1: set this bit for MISO to operate as normal.

8

RXOF

SPIRX overflow overwrite enable.

0x0

RW

0: cleared by user; the new serial byte received is discarded.

1: set by user; the valid data in the Rx register is overwritten by the new

serial byte received.

7

ZEN

Transmit zeros enable.

0x0

RW

0: clear this bit to transmit the last transmitted value when there is no valid

data in the Tx FIFO.

1: set this bit to transmit 0x00 when there is no valid data in the Tx FIFO.