TOSHIBA

TMPR3904F Rev. 2.0

177

16

RDIE

Receive

data DMA

/Interrupt

enable

Receive DMA/Interrupt Enable

When in interrupt mode (SDMAE = 0)

Valid data read request interrupt enable for

receive FIFO. Asserts the SINTREQ* signal

when there is valid data in the receive FIFO.

0:

Disable

1:

Enable

When in DMA mode (SDMAE = 1)

Read DMA request enable. Generates a read

request when the number of valid data in

the receive FIFO reaches the DMA request

trigger level.

0: Asserts the SINTREQ* signal.

1: Asserts the SDMAREQ* signal.

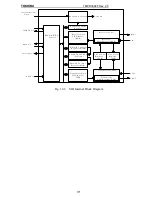

Fig. 12-7 DMA/Interrupt Control Register (2/2)

Summary of Contents for TMPR3904F

Page 1: ...Users Manual 32bit RISC Microprocessor TX39 family TMPR3904F Rev 2 0 Jan 12 1998 ...

Page 2: ......

Page 9: ...Users Manual 01 1 INTRODUCTION 1 1 Overview ...

Page 11: ...Users Manual 03 1 3 Kind of accessing by the TX3904 ...

Page 12: ...Users Manual 04 1 4 Precautions in the TMPR3904F specification Don t set Don t use ...

Page 13: ...Users Manual 05 Do not use ...

Page 14: ...Users Manual 06 ...

Page 15: ...Users Manual 7 2 FEATURES n n n n n n n n n n n n n ...

Page 16: ...Users Manual 8 ...

Page 18: ...Users Manual 10 ...

Page 19: ...Users Manual 11 4 PINS 4 1 Positions of Pins ...

Page 20: ...Users Manual 12 ...

Page 21: ...Users Manual 13 4 2 Functions of Pins ...

Page 22: ...Users Manual 14 ...

Page 23: ...Users Manual 15 ...

Page 24: ...Users Manual 16 ...

Page 26: ...Users Manual 18 5 2 Register Map ...

Page 27: ...Users Manual 19 ...

Page 28: ...Users Manual 20 ...

Page 30: ...Users Manual 22 5 3 2 PIO2 and PIO1 ...

Page 32: ...Users Manual 24 5 3 4 Connection of external bus master 5 3 5 INT 7 0 active status clear ...

Page 33: ...Users Manual 25 5 3 6 INT 7 0 active status set up ...

Page 34: ...Users Manual 26 ...

Page 123: ...TOSHIBA TMPR3904F Rev 2 0 115 26 ...

Page 169: ...TOSHIBA TMPR3904F Rev 2 0 161 26 ...

Page 203: ...TOSHIBA TMPR3904F Rev 2 0 195 ...

Page 230: ......