TOSHIBA

TMPR3904F Rev. 2.0

164

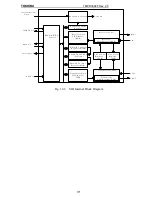

11.3

Functions

11.3.1

Interrupt sources

The TX3904 has the following interrupt sources.

(Maskable) interrupts

Table 11-1 shows the interrupt sources of the TX3904.

The priority of Numbers 0-15 interrupts is arbitrated by the IRC and the interrupt with the

highest priority is informed to the TX39 Processor Core. When one of the Numbers 0-15

interrupts is informed to the TX39 Processor Core, IP[4] in the TX39 Cause register is set and,

as the same time, the interrupt number is indicated in the IP[3:0].

Interrupts by the INT[0] are not arbitrated for the priority unlike the Numbers 0-15 interrupts.

Interrupts by the INT[0] are not masked in the TX3904 internal circuits. When an interrupt by

the INT[0] is informed of, IP[5] is set.

Table 11-1 Interrupt Sources

Interrupt

Number

IP[5:0]

Interrupt Request

Source

Name of Interrupt

15

x11111

TMR2

Timer Interrupt

14

x11110

TMR1

Timer Interrupt

13

x11101

TMR0

Timer Interrupt

12

x11100

SIO1

SIO Interrupt

11

x11011

SIO0

SIO Interrupt

10

x11010

DMAC0

DMA Interrupt (Ch.0)

9

x11001

DMAC0

DMA Interrupt (Ch.1)

8

x11000

DMAC1

DMA Interrupt (Ch.2)

7

x10111

DMAC1

DMA Interrupt (Ch.3)

6

x10110

INT[7]

External Interrupt

5

x10101

INT[6]

External Interrupt

4

x10100

INT[5]

External Interrupt

3

x10011

INT[4]

External Interrupt

2

x10010

INT[3]

External Interrupt

1

x10001

INT[2]

External Interrupt

0

x10000

INT[1]

External Interrupt

1xxxxx

INT[0]

External Interrupt

Non-maskable interrupts

The sources for non-maskable interrupts are divided into the interrupts by the NMI* signal,

watchdog timer interrupts by the TMR2 and bus error in a write operation by the TX39

processor core.

The TX3904 acknowledges falling edges of the NMI* as a non-maskable interrupt request.

The TMR2 requests of the TX39 Coprocessor Core for a non-maskable interrupt if the TMR

requests for a watchdog interrupt in the watchdog timer mode. However, if the WR bit of the

CConR is set to 1, reset is implemented to the TX3904 at a watchdog interrupt time.

Summary of Contents for TMPR3904F

Page 1: ...Users Manual 32bit RISC Microprocessor TX39 family TMPR3904F Rev 2 0 Jan 12 1998 ...

Page 2: ......

Page 9: ...Users Manual 01 1 INTRODUCTION 1 1 Overview ...

Page 11: ...Users Manual 03 1 3 Kind of accessing by the TX3904 ...

Page 12: ...Users Manual 04 1 4 Precautions in the TMPR3904F specification Don t set Don t use ...

Page 13: ...Users Manual 05 Do not use ...

Page 14: ...Users Manual 06 ...

Page 15: ...Users Manual 7 2 FEATURES n n n n n n n n n n n n n ...

Page 16: ...Users Manual 8 ...

Page 18: ...Users Manual 10 ...

Page 19: ...Users Manual 11 4 PINS 4 1 Positions of Pins ...

Page 20: ...Users Manual 12 ...

Page 21: ...Users Manual 13 4 2 Functions of Pins ...

Page 22: ...Users Manual 14 ...

Page 23: ...Users Manual 15 ...

Page 24: ...Users Manual 16 ...

Page 26: ...Users Manual 18 5 2 Register Map ...

Page 27: ...Users Manual 19 ...

Page 28: ...Users Manual 20 ...

Page 30: ...Users Manual 22 5 3 2 PIO2 and PIO1 ...

Page 32: ...Users Manual 24 5 3 4 Connection of external bus master 5 3 5 INT 7 0 active status clear ...

Page 33: ...Users Manual 25 5 3 6 INT 7 0 active status set up ...

Page 34: ...Users Manual 26 ...

Page 123: ...TOSHIBA TMPR3904F Rev 2 0 115 26 ...

Page 169: ...TOSHIBA TMPR3904F Rev 2 0 161 26 ...

Page 203: ...TOSHIBA TMPR3904F Rev 2 0 195 ...

Page 230: ......