Appendix B Internal I/O Registers

Rev. 6.00 Sep 12, 2006 page 479 of 526

REJ09B0326-0600

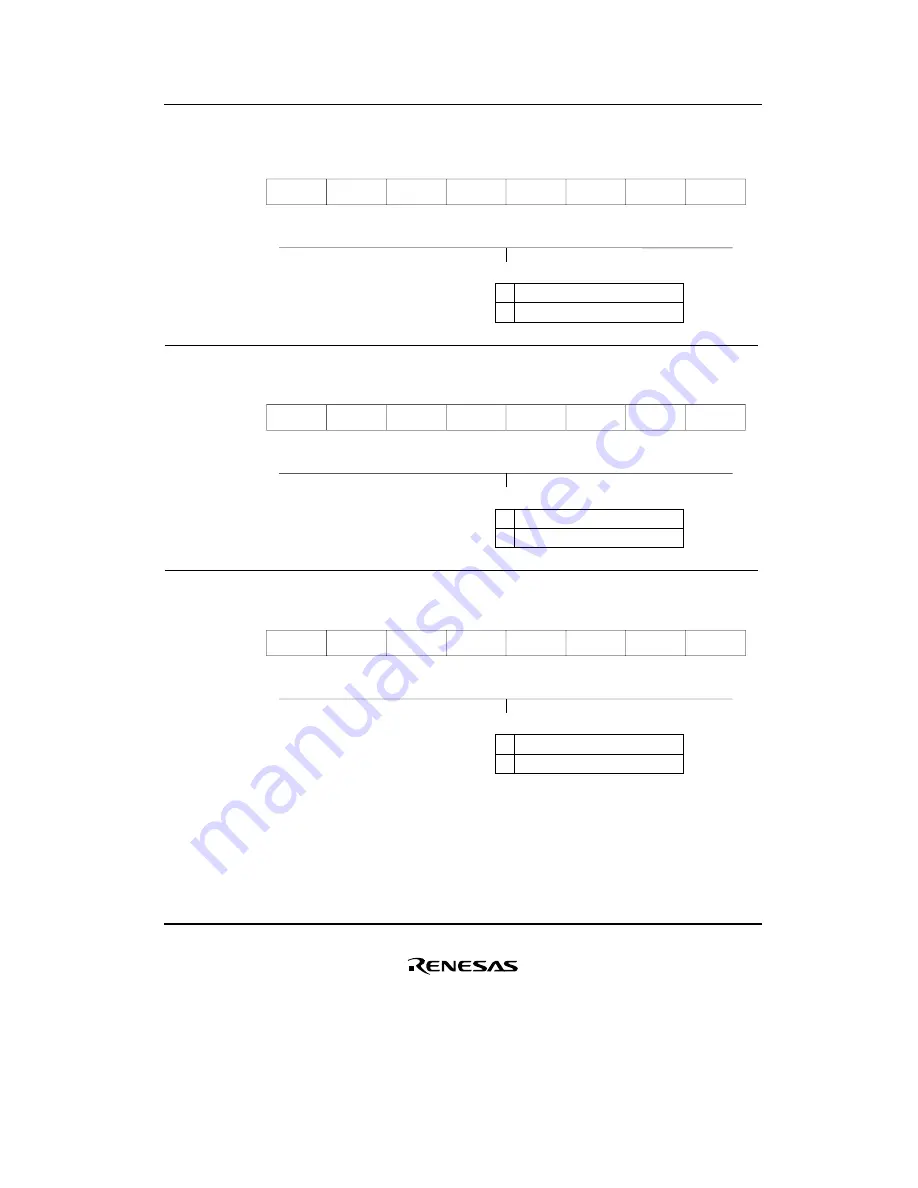

PCR1—Port control register 1

H'FFE4

I/O ports

Bit

Initial value

Read/Write

7

PCR1

0

W

6

PCR1

0

W

5

PCR1

0

W

4

PCR1

0

W

3

—

0

—

0

PCR1

0

W

2

—

0

—

1

—

0

—

Port 1 input/output select

0

Input pin

1

Output pin

7

6

5

4

0

PCR2—Port control register 2

H'FFE5

I/O ports

Bit

Initial value

Read/Write

7

—

0

—

6

—

0

—

5

—

0

—

4

—

0

—

3

—

0

—

0

PCR2

0

W

2

PCR2

0

W

1

PCR2

0

W

Port 2 input/output select

0

Input pin

1

Output pin

0

2

1

PCR3—Port control register 3

H'FFE6

I/O ports

Bit

Initial value

Read/Write

7

—

0

—

6

—

0

—

5

—

0

—

4

—

0

—

3

—

0

—

0

PCR3

0

W

2

PCR3

0

W

1

PCR3

0

W

Port 3 input/output select

0

Input pin

1

Output pin

0

2

1

Summary of Contents for F-ZTAT H8/3642A Series

Page 6: ...Rev 6 00 Sep 12 2006 page iv of xx ...

Page 8: ...Rev 6 00 Sep 12 2006 page vi of xx ...

Page 22: ...Rev 6 00 Sep 12 2006 page xx of xx ...

Page 124: ...Section 5 Power Down Modes Rev 6 00 Sep 12 2006 page 102 of 526 REJ09B0326 0600 ...

Page 188: ...Section 6 ROM Rev 6 00 Sep 12 2006 page 166 of 526 REJ09B0326 0600 ...

Page 190: ...Section 7 RAM Rev 6 00 Sep 12 2006 page 168 of 526 REJ09B0326 0600 ...

Page 298: ...Section 9 Timers Rev 6 00 Sep 12 2006 page 276 of 526 REJ09B0326 0600 ...

Page 378: ...Section 12 A D Converter Rev 6 00 Sep 12 2006 page 356 of 526 REJ09B0326 0600 ...

Page 446: ...Section 13 Electrical Characteristics Rev 6 00 Sep 12 2006 page 424 of 526 REJ09B0326 0600 ...