Basics communication

EL5101, EL5101-0010, EL5101-0011

30

Version: 4.2

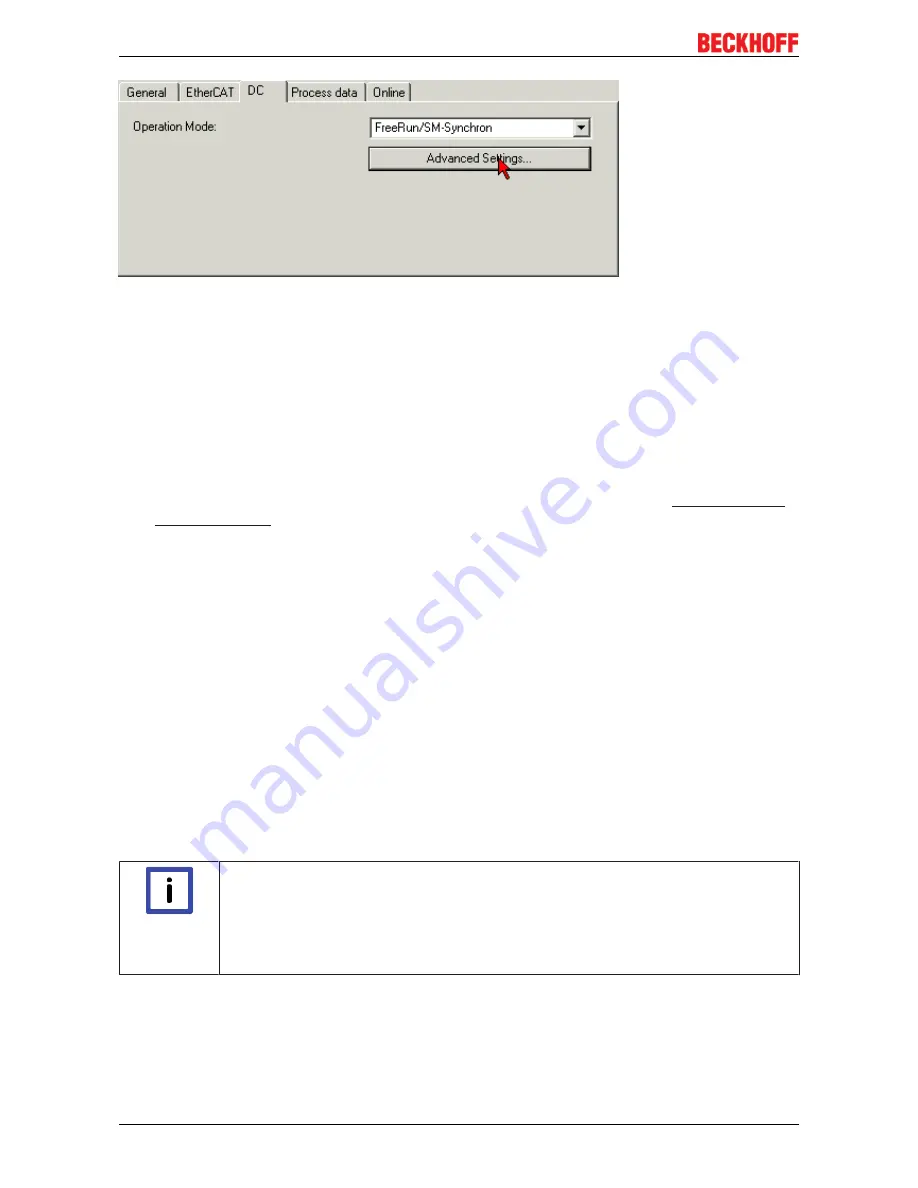

Fig. 19: “DC” tab (Distributed Clocks)

•

FreeRun/SM-Synchron

The SynManager event occurs when an EtherCAT frame successfully exchanges process data with

the EL51xx. Frame-triggered, the current counter value is thus cyclically determined, but with the low

temporal jitter of the Ethernet frame. In this mode an Ethernet frame triggers the process data provision

for the

next

retrieving frame. This generally only occurs after 1x cycle time.

•

DC Synchronous

In DC mode, a counter reading is triggered by the integrated DC unit with a constant cycle, usually in

synchrony with the bus cycle, although with a constant shift (phase, shift time, offset). Sampling is

significantly more uniform (synchronization accuracy: 100 ns), which means a higher-level control

algorithm can be supplied with higher-quality position data, for example. In the EL51xx the trigger is the

SYNC0 signal, which is set like an output component in “DC-synchron” mode. See

Distributed Clocks

system description

.

The DC modes enable the start time of the process data provision to be offset by an offset value (shift

value). This offset value can only by set on EtherCAT startup and can then no longer be changed

during the uptime. Based on the general distributed clocks SYNC function model, the terminal-specific

SYNC signal can either occur

before

or

after

the expect frame pass-through time: For input terminals

the SYNC signal is generated

before

the frame, in order to make current input data available for

forwarding. For output terminals the SYNC signal is set to a time

after

the frame has passed through,

so that the just supplied data are output immediately. Since only one of the two modes is possible, the

user can set the optimum mode for his application.

"DC Synchronous" corresponds to the output module configuration. The local SYNC event is triggered

shortly after the EtherCAT frame has passed.

•

DC-Synchron (input based)

In the “DC-Synchronous (input based)” mode this EL51xx is assigned to the group of input modules

and the shift time (see Fig.

Advanced Distributed Clock (DC) settings, EL51xx terminal

) is calculated

accordingly.

When “DC-Synchronous” operating mode is activated, TwinCAT selects settings that ensure reliable

operation of the EL51xx and the acquisition of current position data. This means that determination of the

current counter value is started by the SYNC0 signal at highly constant intervals and in the operating mode

“DC-Synchronous (input based)” in good time – i.e. with an adequate safety buffer – before the retrieving

EtherCAT datagram.

Note

Duration of the process data provision in the EL51x1

The EL5101 (from Hardware 09 / Firmware 14) or the EL5151 (from Hardware 01/

Firmware 05) requires approx. 80 µs after the SYNC event to determine the position data

and provide them for retrieval. This value depends on the configuration and parameteriza-

tion. The actual current duration can be read using the internal DC functions, see CoE set-

ting in 1C32:08 and the result in 1C32:05.

If necessary, the SYNC0 signal can be shifted along the time axis to the right/later or left/earlier in associated

dialogs by specifying a “User defined Shift Time”, see Fig.

Advanced Distributed Clock (DC) settings, EL51xx

terminal.

Summary of Contents for EL5101

Page 2: ......