AXI Bridge for PCI Express v2.4

12

PG055 June 4, 2014

Chapter 2:

Product Specification

Port Descriptions

The interface signals for the AXI Bridge for PCI Express are described in

.

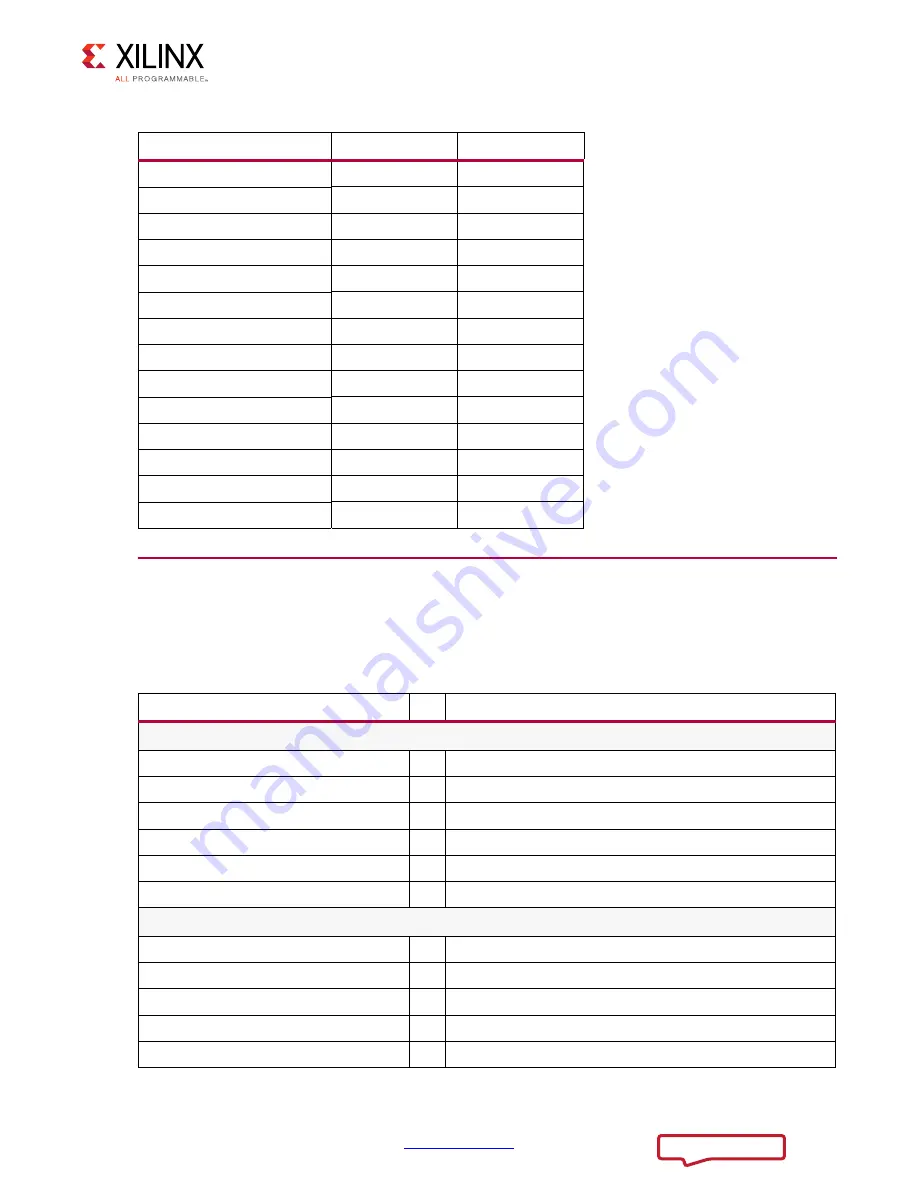

Table 2-2:

Resource Utilization Summary

Configuration

Slice Registers

Slice LUTs

Endpoint x1 Gen1

8678

13054

Endpoint x2 Gen1

8963

13300

Endpoint x4 Gen1

9558

13666

Endpoint x8 Gen1

11912

17355

Endpoint x1 Gen2

8620

14041

Endpoint x2 Gen2

8897

14362

Endpoint x4 Gen2

10629

16477

Root Port x1 Gen1

10703

15909

Root Port x2 Gen1

10836

15537

Root Port x4 Gen1

11431

15924

Root Port x8 Gen1

13805

20128

Root Port x1 Gen2

10674

16734

Root Port x2 Gen2

11062

17137

Root Port x4 Gen2

12563

19325

Table 2-3:

Top-Level Interface Signals

Signal Name

I/O Description

Global Signals

refclk

I

PCIe Reference Clock

axi_aresetn

I

Global reset signal for AXI Interfaces

axi_aclk_out

O PCIe derived clock output for axi_aclk

axi_ctl_aclk_out

O PCIe derived clock output for axi_ctl_aclk

mmcm_lock

O axi_aclk_out from the axi_enhanced_pcie block is stable

interrupt_out

O Interrupt signal

AXI Slave Interface

s_axi_awid[c_s_axi_id_width-1:0]

I

Slave write address ID

s_axi_awaddr[c_s_axi_addr_width-1:0]

I

Slave address write

s_axi_awregion[3:0]

I

Slave write region decode

s_axi_awlen[7:0]

I

Slave write burst length

s_axi_awsize[2:0]

I

Slave write burst size