AXI Bridge for PCI Express v2.4

13

PG055 June 4, 2014

Chapter 2:

Product Specification

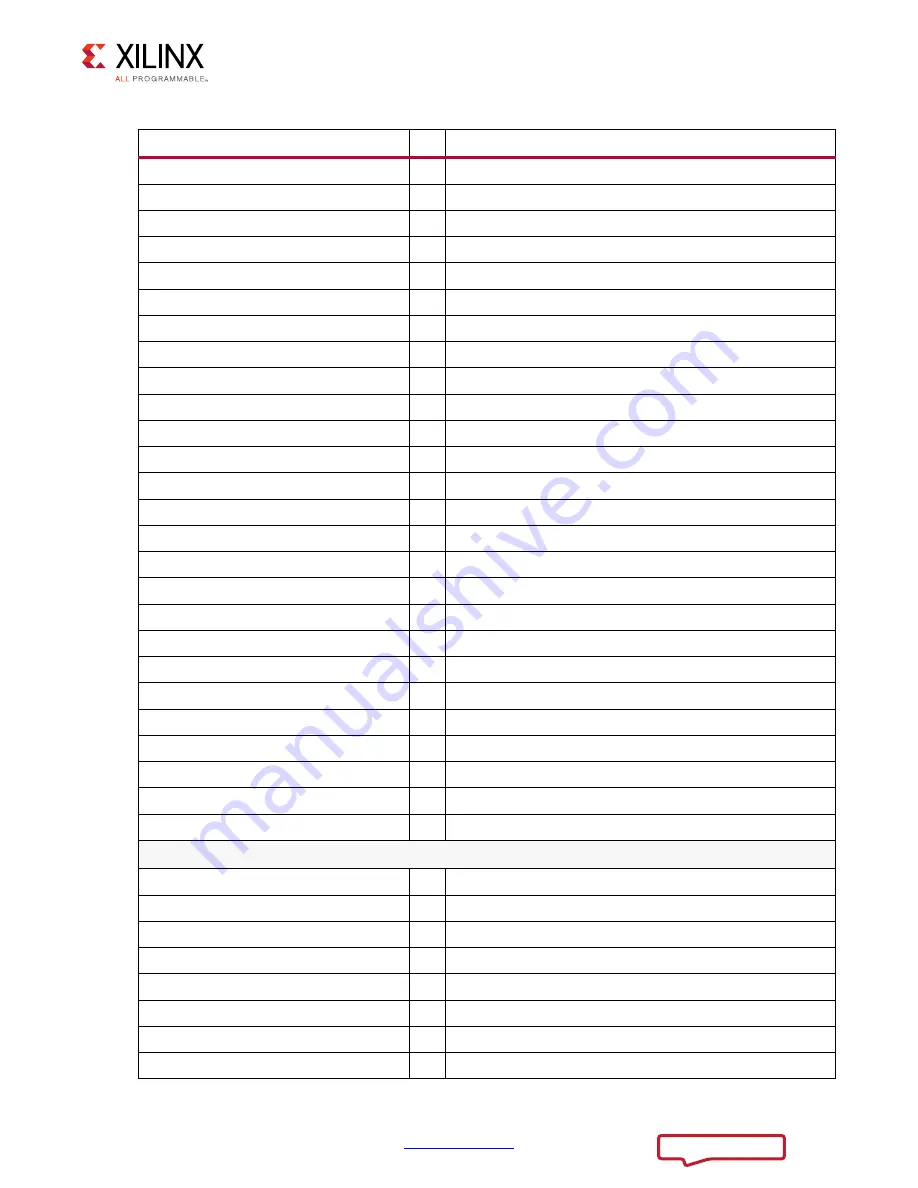

s_axi_awburst[1:0]

I

Slave write burst type

s_axi_awvalid

I

Slave address write valid

s_axi_awready

O Slave address write ready

s_axi_wdata[c_s_axi_data_width-1:0]

I

Slave write data

s_axi_wstrb[c_s_axi_data_width/8-1:0]

I

Slave write strobe

s_axi_wlast

I

Slave write last

s_axi_wvalid

I

Slave write valid

s_axi_wready

O Slave write ready

s_axi_bid[c_s_axi_id_width-1:0]

O Slave response ID

s_axi_bresp[1:0]

O Slave write response

s_axi_bvalid

O Slave write response valid

s_axi_bready

I

Slave response ready

s_axi_arid[c_s_axi_id_width-1:0]

I Slave read address ID

s_axi_araddr[c_s_axi_addr_width-1:0]

I Slave read address

s_axi_arregion[3:0]

I

Slave read region decode

s_axi_arlen[7:0]

I

Slave read burst length

s_axi_arsize[2:0]

I

Slave read burst size

s_axi_arburst[1:0]

I

Slave read burst type

s_axi_arvalid

I

Slave read address valid

s_axi_arready

O Slave read address ready

s_axi_rid[c_s_axi_id_width-1:0]

O Slave read ID tag

s_axi_rdata[c_s_axi_data_width-1:0]

O Slave read data

s_axi_rresp[1:0]

O Slave read response

s_axi_rlast

O Slave read last

s_axi_rvalid

O Slave read valid

s_axi_rready

I

Slave read ready

AXI Master Interface

m_axi_awaddr[c_m_axi_addr_width-1:0]

O Master address write

m_axi_awlen[7:0]

O Master write burst length

m_axi_awsize[2:0]

O Master write burst size

m_axi_awburst[1:0]

O Master write burst type

m_axi_awprot[2:0]

O Master write protection type

m_axi_awvalid

O Master write address valid

m_axi_awready

I

Master write address ready

m_axi_wdata[c_m_axi_data_width-1:0]

O Master write data

Table 2-3:

Top-Level Interface Signals

(Cont’d)

Signal Name

I/O Description