AXI Bridge for PCI Express v2.4

102

PG055 June 4, 2014

Appendix B:

Debugging

Identifying Errors

See

Abnormal Conditions in Chapter 3

for information about how the Slave side and Master

side of the AXI Bridge for PCI Express handle abnormal conditions.

Next Steps

If the debug suggestions listed previously do not resolve the issue, open a support case or

visit the Xilinx User Community forums to have the appropriate Xilinx expert assist with the

issue.

To create a technical support case in WebCase, see the Xilinx website at:

www.xilinx.com/support/clearexpress/websupport.htm

Items to include when opening a case:

°

Detailed description of the issue and results of the steps listed above.

°

Vivado lab tools captures taken in the steps above.

To discuss possible solutions, use the Xilinx User Community:

Transceiver Debug

describes the ports used to debug transceiver related issues.

RECOMMENDED:

Debugging transceiver issues is recommended for advanced users only.

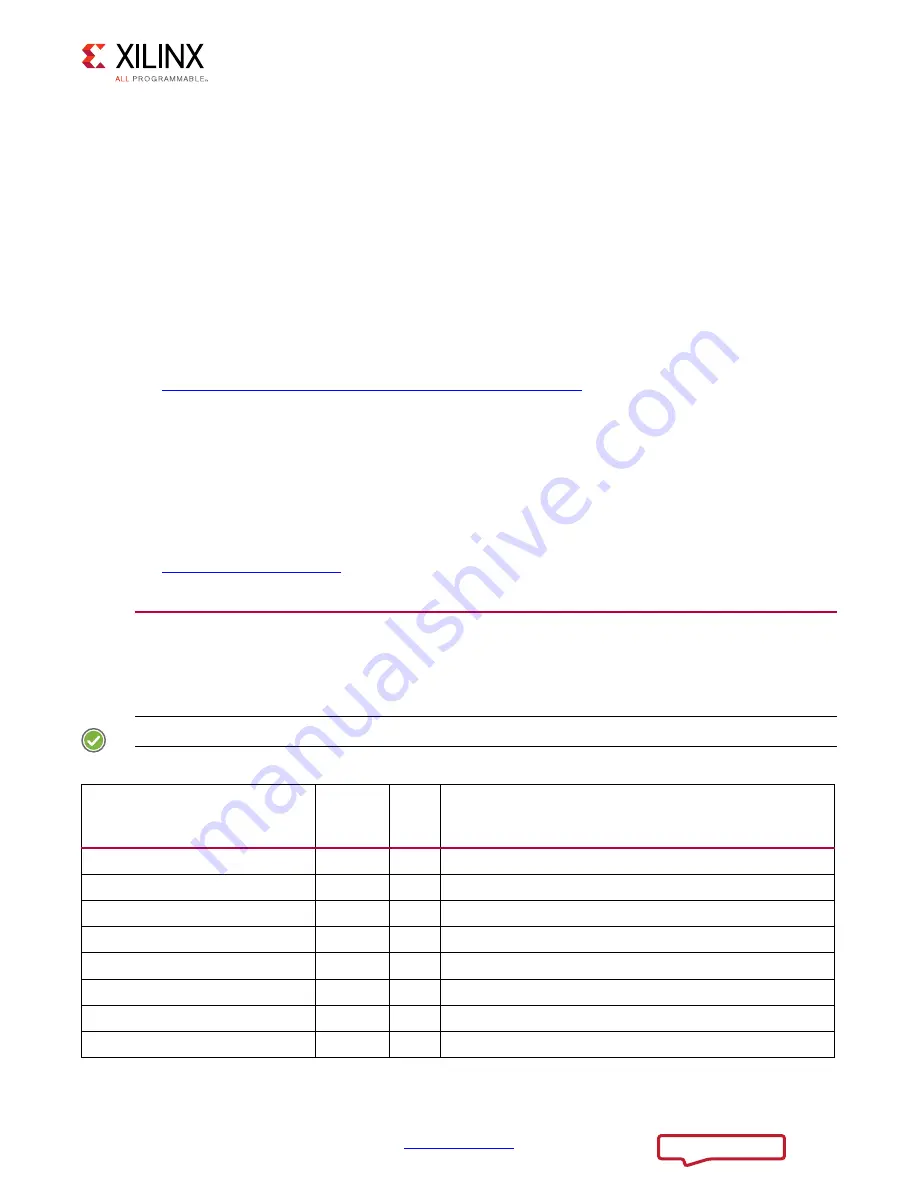

Table B-1:

Ports Used for Transceiver Debug

Port

Direction Width

Description

pipe_txprbssel

I

3

PRBS input.

pipe_rxprbssel

I

3

PRBS input.

pipe_rxprbsforceerr

I

1

PRBS input.

pipe_rxprbscntrreset

I

1

PRBS input.

pipe_loopback

I

1

PIPE loopback.

pipe_rxprbserr

O

1

PRBS output.

pipe_rst_fsm

O

Should be examined if

pipe_rst_idle

is stuck at 0.

pipe_qrst_fsm

O

Should be examined if

pipe_rst_idle

is stuck at 0.