AXI Bridge for PCI Express v2.4

38

PG055 June 4, 2014

Chapter 2:

Product Specification

AXI Base Address Translation Configuration Registers (Offset

0x208 - 0x234)

The AXI Base Address Translation Configuration Registers and their offsets are shown in

and the register bits are described in

. This set of registers can be used

in two configurations based on the top-level parameter C_AXIBAR_AS_n. When the BAR is

set to a 32-bit address space, then the translation vector should be placed into the

AXIBAR2PCIEBAR_nL register where n is the BAR number. When the BAR is set to a 64-bit

address space, then the most significant 32 bits are written into the AXIBAR2PCIEBAR_nU

and the least significant 32 bits are written into AXIBAR2PCIEBAR_nL. These registers are

only included if C_INCLUDE_BAR_OFFSET_REG = 1.

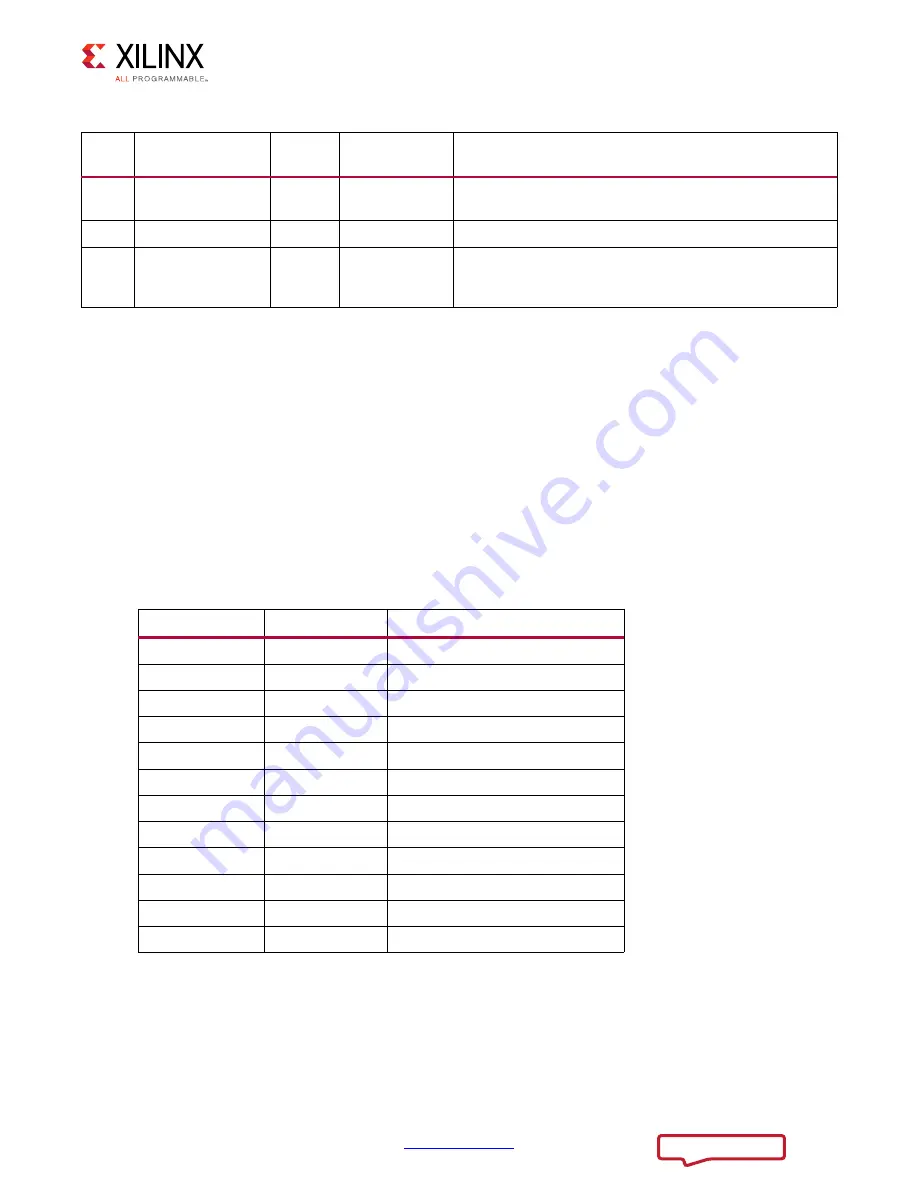

Table 2-23:

VSEC Header Register 2

Bits

Name

Core

Access

Reset Value

Description

15:0

VSEC ID

RO

0x0002

ID value uniquely identifying the nature and format of

this VSEC structure.

19:16 VSEC REV

RO

0x0

Version of this capability structure. Hardcoded to 0x0.

31:20 VSEC Length

RO

0x038

Length of the entire VSEC Capability structure, in bytes,

including the VSEC Capability register. Hardcoded to

0x038 (56 decimal).

Table 2-24:

AXI Base Address Translation Configuration Registers

Offset

Bits

Register Mnemonic

0x208

31-0

AXIBAR2PCIEBAR_0U

0x20C

31-0

AXIBAR2PCIEBAR_0L

0x210

31-0

AXIBAR2PCIEBAR_1U

0x214

31-0

AXIBAR2PCIEBAR_1L

0x218

31-0

AXIBAR2PCIEBAR_2U

0x21C

31-0

AXIBAR2PCIEBAR_2L

0x220

31-0

AXIBAR2PCIEBAR_3U

0x224

31-0

AXIBAR2PCIEBAR_3L

0x228

31-0

AXIBAR2PCIEBAR_4U

0x22C

31-0

AXIBAR2PCIEBAR_4L

0x230

31-0

AXIBAR2PCIEBAR_5U

0x234

31-0

AXIBAR2PCIEBAR_5L