AXI Bridge for PCI Express v2.4

18

PG055 June 4, 2014

Chapter 2:

Product Specification

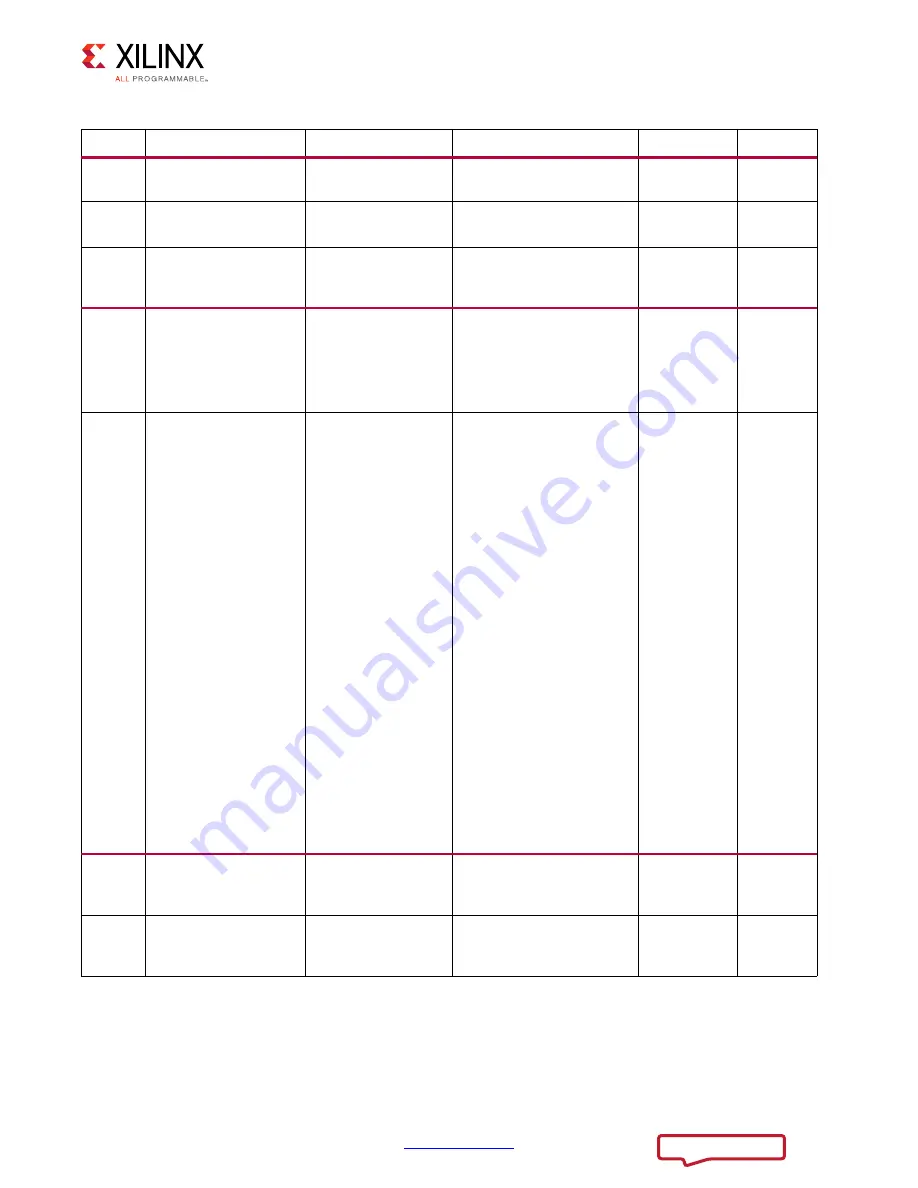

G28

C_AXIBAR_

HIGHADDR_5

AXI BAR_5 aperture

high address

Valid AXI address

0x0000_0000 std_logic_

vector

G29

C_AXIBAR_AS_5

AXI BAR_5 address

size

0: 32 bit

1: 64 bit

0

Integer

G30

C_AXIBAR2PCIEBAR_5

PCIe BAR to which

AXI BAR_5 is

mapped

Valid address for PCIe

0xFFFF_FFFF std_logic_

vector

G31

C_PCIEBAR_NUM

Number of address

for PCIe apertures

that can be accessed

1-3;

1: BAR_0 enabled

2: BAR_0, BAR_1 enabled

3: BAR_0, BAR_1, BAR_2

enabled

3

Integer

G32

C_PCIEBAR_AS

Configures PCIEBAR

aperture width to be

32 bits wide or 64

bits wide

0: Generates three 32-bit

PCIEBAR address

apertures.

32-bit BAR example:

PCIEBAR_0 is 32 bits

PCIEBAR_1 is 32 bits

PCIEBAR_2 is 32 bits

1: Generates three 64 bit

PCIEBAR address

apertures.

64-bit BAR example:

PCIEBAR_0 and PCIEBAR_1

concatenate to comprise

64-bit PCIEBAR_0.

PCIEBAR_2 and PCIEBAR_3

concatenate to comprise

64-bit PCIEBAR_1.

PCIEBAR_4 and PCIEBAR_5

concatenate to comprise

64-bit PCIEBAR_2

1

Integer

G33

C_PCIEBAR_LEN_0

Power of 2 in the

size of bytes of PCIE

BAR_0 space

13-31

16

Integer

G34

C_PCIEBAR2AXIBAR_0

AXIBAR to which

PCIE BAR_0 is

mapped

Valid AXI address

0x0000_0000 std_logic_

vector

Table 2-4:

Top-Level Parameters

(Cont’d)

Generic

Parameter Name

Description

Allowable Values

Default Value VHDL Type