AXI Bridge for PCI Express v2.4

20

PG055 June 4, 2014

Chapter 2:

Product Specification

C_S_AXI_CTL_

PROTOCOL

AXI4-Lite port

connection

definition to AXI

Interconnect in the

Vivado IP integrator.

AXI4LITE

AXI4LITE

String

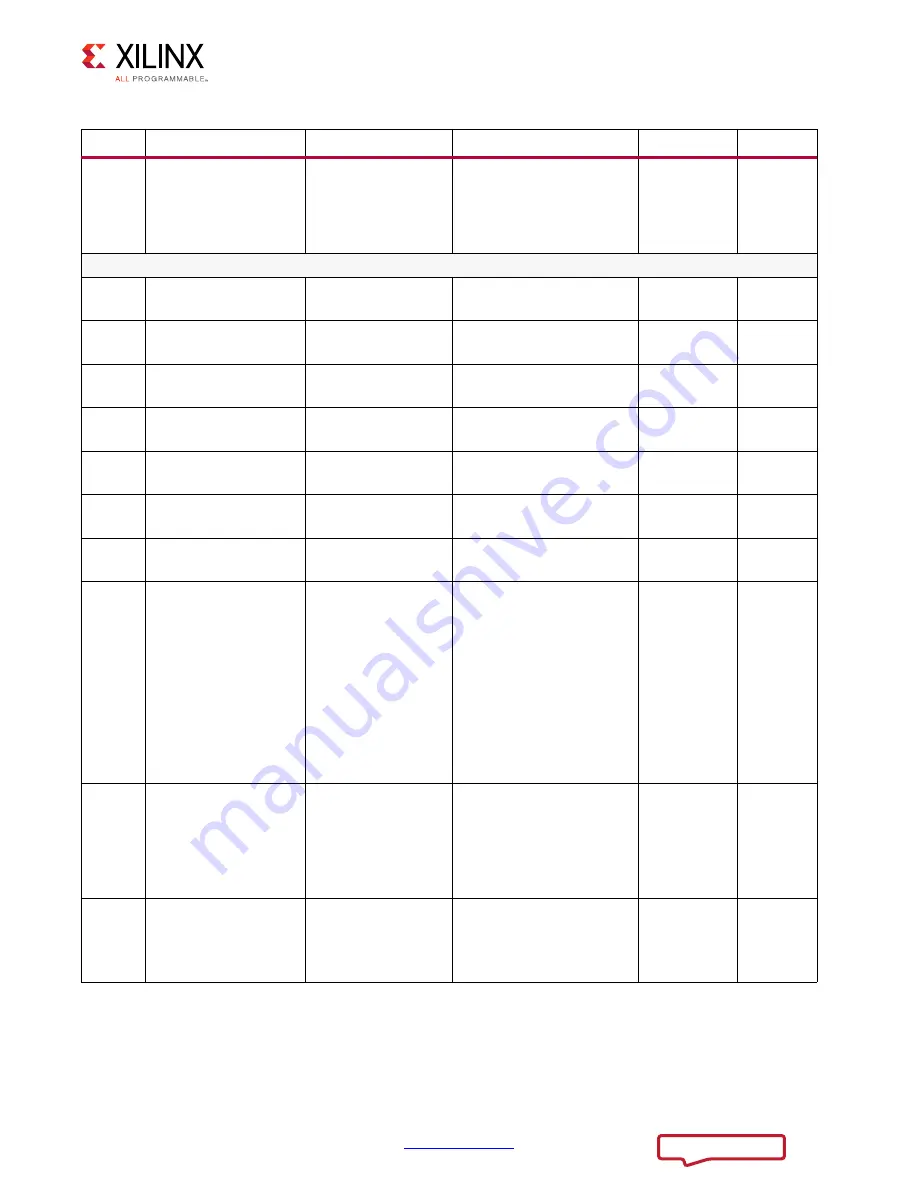

Core for PCIe Configuration Parameters

G41

C_NO_OF_LANES

Number of PCIe

Lanes

1, 2, 4, 8: 7 series FPGAs

1

Integer

G42

C_DEVICE_ID

Device ID

16-bit vector

0x0000

std_logic_

vector

G43

C_VENDOR_ID

Vendor ID

16-bit vector

0x0000

std_logic_

vector

G44

C_CLASS_CODE

Class Code

24-bit vector

0x00_0000

std_logic_

vector

G45

C_REV_ID

Rev ID

8-bit vector

0x00

std_logic_

vector

G46

C_SUBSYSTEM_ID

Subsystem ID

16-bit vector

0x0000

std_logic_

vector

G47

C_SUBSYSTEM_

VENDOR_ID

Subsystem Vendor

ID

16-bit vector

0x0000

std_logic_

vector

C_PCIE_USE_MODE

Specifies PCIe use

mode for underlying

serial transceiver

wrapper usage/

configuration

(specific only to 7

series).

This parameter

ignored for

Zynq-7000 devices

(set to 3.0).

See

.

1.0: For Kintex-7 325T IES

(initial ES) silicon

1.1: For Virtex-7 485T IES

(initial ES) silicon

3.0: For GES (general ES)

silicon

1.0

String

G48

C_PCIE_CAP_SLOT_

IMPLEMENTED

PCIE Capabilities

Register Slot

Implemented

0: Not add-in card slot

1: Downstream port is

connected to add-in card

slot

(valid only for Root

Complex)

0

Integer

G49

C_REF_CLK_FREQ

REFCLK input

Frequency

0: 100 MHz

1: 125 MHz

2: 250 MHz - 7 series

FPGAs only

0

Integer

Table 2-4:

Top-Level Parameters

(Cont’d)

Generic

Parameter Name

Description

Allowable Values

Default Value VHDL Type