AXI Bridge for PCI Express v2.4

11

PG055 June 4, 2014

Chapter 2:

Product Specification

frequency, the AXI data width, the number of lanes, and Gen1 (2.5 GT/s) or Gen2 (5.0 GT/s)

link speed.

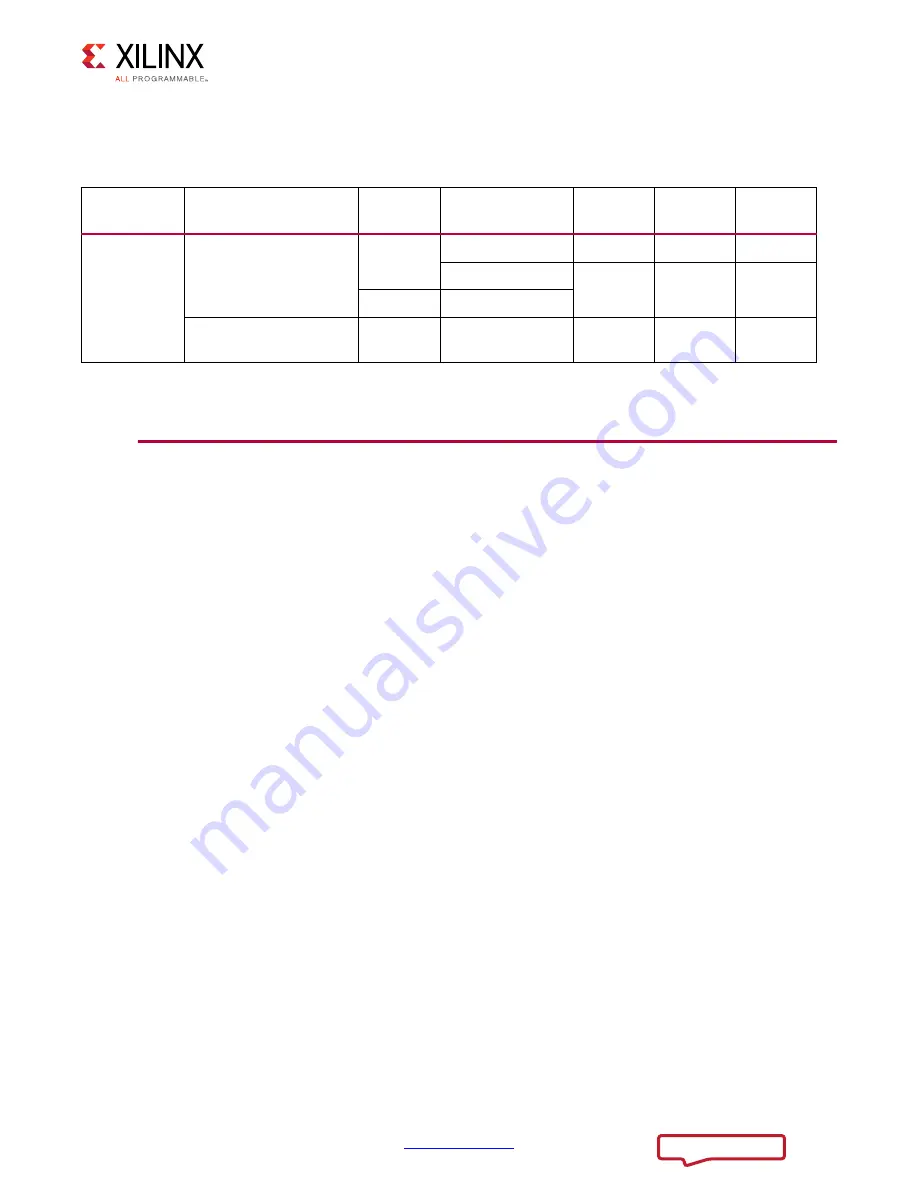

Resource Utilization

illustrates a subset of IP core configurations and the device utilization estimates.

Variation in tools and optimization settings can result in variance of these reported

numbers.

shows the resource utilization for the AXI Bridge for PCIe core for different

configurations on the Virtex-7 XC7V2000T device. These numbers were generated in the

Vivado® Design Suite. Resource Utilization numbers for other devices can be generated by

implementing the provided example design and checking for the resources used by only

the core in the resource utilization report.

Table 2-1:

Line Rate for PCIe Support for Gen1/Gen2

C_FAMILY

C_X_AXI_DATA_WIDTH PCIe Link

Speed

C_NO_OF_LANES AXI_ACLK

_OUT

Userclk1

Userclk2

7 series,

Zynq

®

-7000

64

Gen1

x1

62.5 MHz

62.5 MHz

62.5 MHz

x2, 4

125 MHz

125 MHz

125 MHz

Gen2

x1, 2

128

Gen1,

Gen2

x1, 2, 4, 8

125 MHz

250 MHz

125 MHz

Notes:

1. x8 Gen2 configuration is not supported. Artix-7 does not support x8 Gen1.