AXI Bridge for PCI Express v2.4

98

PG055 June 4, 2014

Appendix B:

Debugging

FPGA Configuration Time Debug

Device initialization and configuration issues can be caused by not having the FPGA

configured fast enough to enter link training and be recognized by the system. Section 6.6

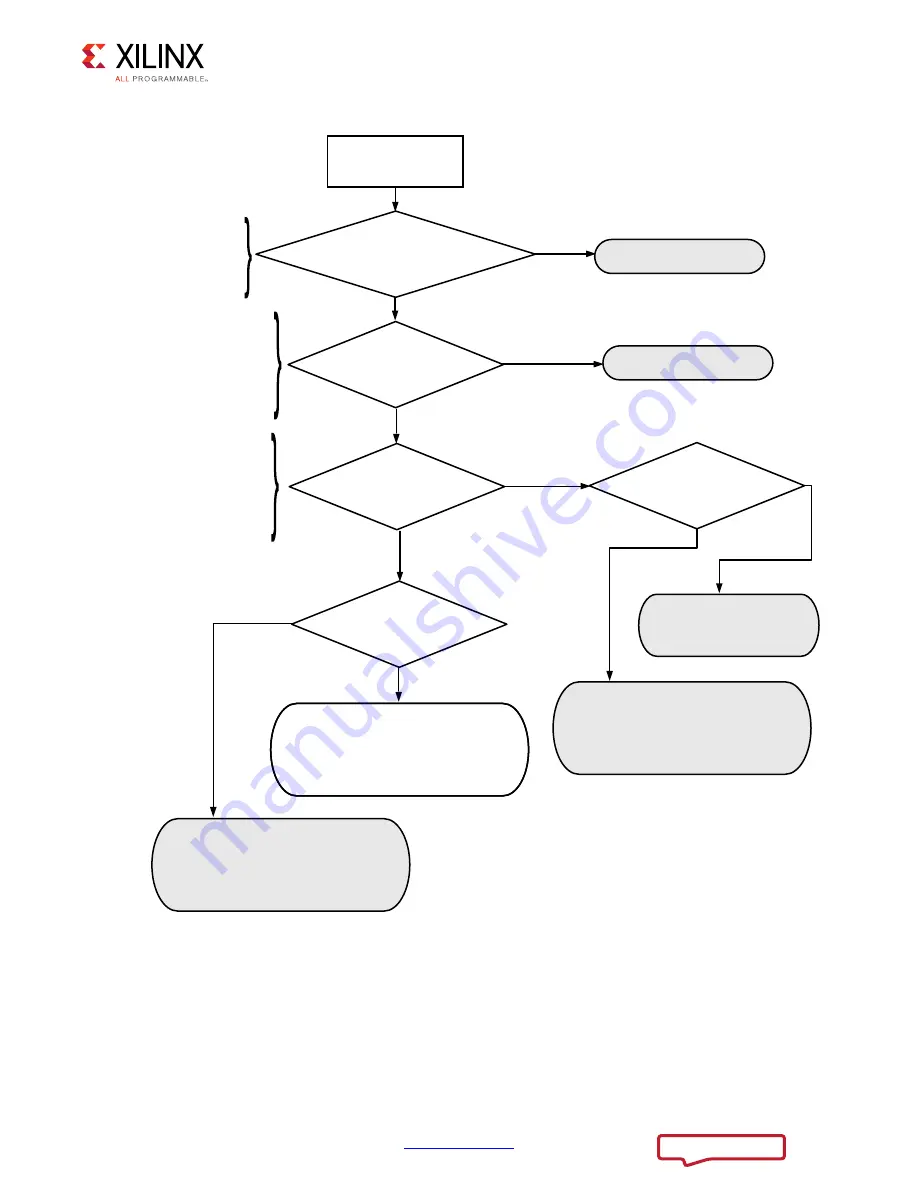

X-Ref Target - Figure B-5

Figure B-5:

Link Trained Debug Flow Diagram

,INKIS4RAINING

USER?LNK?UP

)STHEDEVICERECOGNIZEDBYTHESYSTEM

#ANITBESEENBY0#)42%%7INDOWS OR

LSPCI,INUX

$OESASOFTRESETFIXTHEPROBLEM

USER?LNK?UP

1R

4OELIMINATE&0'!CONFIGURATION

ASAROOTCAUSEPERFORMASOFT

RESTARTOFTHESYSTEM0ERFORMINGA

SOFTRESETONTHESYSTEMKEEPS

POWERAPPLIEDANDFORCES

REENUMERATIONOFTHEDEVICE

)FTHISFIXESTHEPROBLEMTHENITIS

LIKELYTHE&0'!ISNOTCONFIGUREDIN

TIMEFORTHEHOSTTOACCESSTHECARD

<HV

<HV

$OESUSINGTHEDEFAULTEXAMPLE

DESIGNFIXTHEPROBLEM

1R

1R

1R

'R\RXKDYHDOLQNDQDO\]HU"

$OESMIRRORINGTHE

DEFAULTEXAMPLEDESIGNSETTINGSFOR

THEUSERDESIGNFIXTHEPROBLEM

0#)42%%ANDLSPCISCANTHE

THESYSTEMANDDISPLAYDEVICES

RECOGNIZEDDURINGSTARTUP4HESE

TOOLSSHOWTHE0#)CONFIGURATION

SPACEANDITSSETTINGSWITHIN

THEDEVICE

<HV

4HEDEFAULTEXAMPLEDESIGNISKNOWN

TOWORK/FTENTHEDEFAULTDESIGNWORKS

WHENAUSERDESIGNDOESNOT4HIS

USUALLYINDICATESSOMEPARAMETEROR

RESOURCECONFLICTDUETOSETTINGSUSED

FORTHEUSERDESIGNCONFIGURATION

)TISRECOMMENDEDTOMIRRORTHEDEFAULT

'5)SETTINGSINTOTHEUSERDESIGN

%VENTHOUGHTHEDESIGNMIGHTNOT

FUNCTIONITSHOULDSTILLBERECOGNIZED

BYTHESYSTEM

<HV

#HECKFORCONFIGURATIONSETTINGS

CONFLICT3EETHE$EBUGGING

0#)#ONFIGURATION3PACE0ARAMETERS

SECTION

<HV

)FTHEDEFAULTEXAMPLEDESIGNWORKSBUTMIRRORINGTHE

CONFIGURATIONPARAMETERSDOESNOTFIXTHE

PROBLEMTHENATTENTIONSHOULDBEFOCUSEDON

THEUSERAPPLICATIONDESIGN3EETHE!PPLICATION

2EQUIREMENTSSECTION

1R

7ITHNOLINKANALYZERITISPOSSIBLETOUSE

THE6IVADOLABTOOLSTOGATHERTHESAMEINFORMATION

3EE&0'!#ONFIGURATION4IME

$EBUGSECTION

)TISLIKELYTHEPROBLEMISDUETOTHEDEVICE

NOTRESPONDINGPROPERLYTOSOMETYPEOFACCESS!

LINKANALYZERALLOWSTHEUSERTOVIEWTHELINKTRAFFIC

ANDDETERMINEIFSOMETHINGISINCORRECT3EE

THE5SINGA,INK!NALYZERTO$EBUG

$EVICE2ECOGNITION)SSUESvSECTION

3EEh$ATA4RANSFER&AILING$EBUGv

SECTION

8