AXI Bridge for PCI Express v2.4

32

PG055 June 4, 2014

Chapter 2:

Product Specification

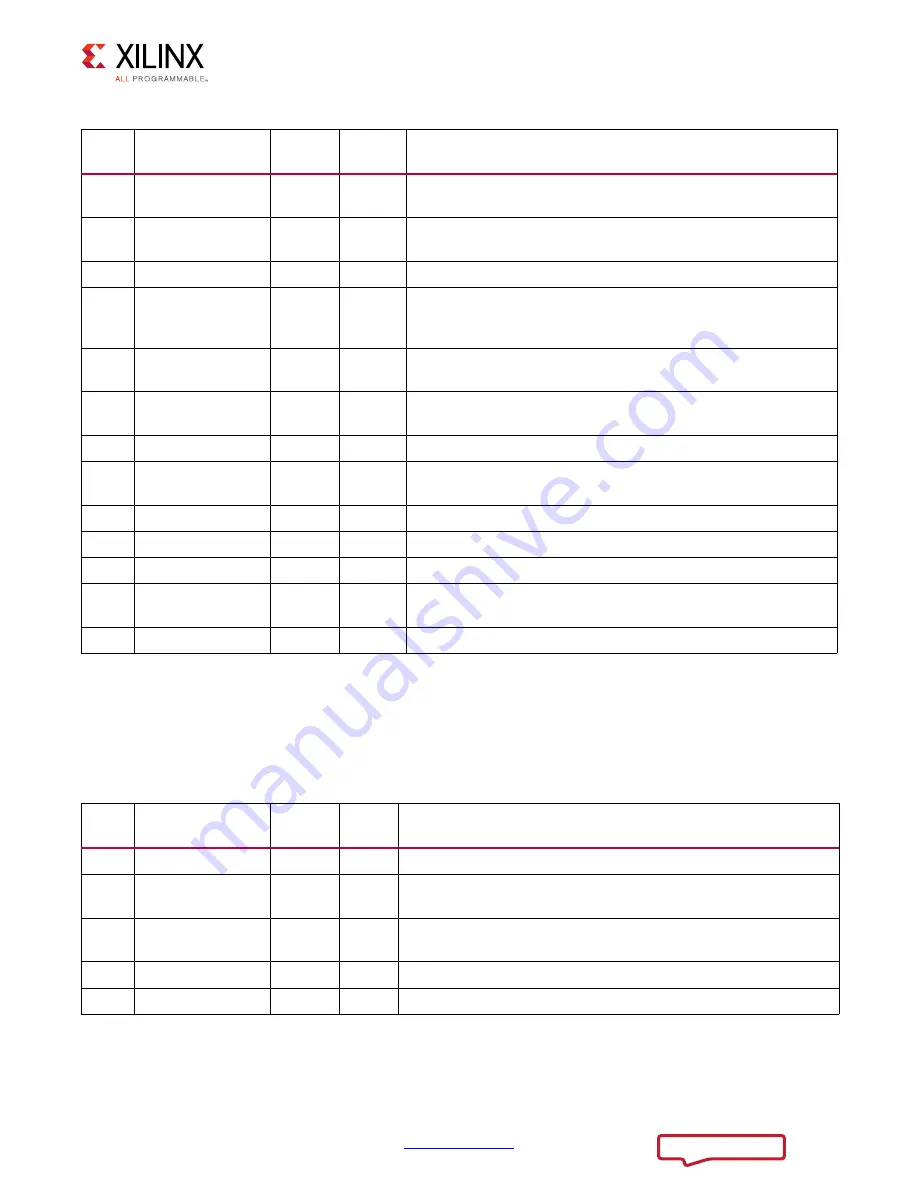

Bus Location Register (Offset 0x140)

The Bus Location register reports the Bus, Device, and Function number, and the Port

number for the PCIe port (

).

16

INTx Interrupt

Received

RO

0

Enables interrupts for INTx Interrupt events when bit is set.

(Only writable for Root Port Configurations, otherwise =0)

17

MSI Interrupt

Received

RO

0

Enables interrupts for MSI Interrupt events when bit is set.

(Only writable for Root Port Configurations, otherwise =0)

19:18 Reserved

RO

0

Reserved

20

Slave

Unsupported

Request

RW

0

Enables the Slave Unsupported Request interrupt when bit is

set.

21

Slave Unexpected

Completion

RW

0

Enables the Slave Unexpected Completion interrupt when bit is

set.

22

Slave Completion

Timeout

RW

0

Enables the Slave Completion Timeout interrupt when bit is set.

23

Slave Error Poison

RW

0

Enables the Slave Error Poison interrupt when bit is set.

24

Slave Completer

Abort

RW

0

Enables the Slave Completer Abort interrupt when bit is set.

25

Slave Illegal Burst

RW

0

Enables the Slave Illegal Burst interrupt when bit is set.

26

Master DECERR

RW

0

Enables the Master DECERR interrupt when bit is set.

27

Master SLVERR

RW

0

Enables the Master SLVERR interrupt when bit is set.

28

Master Error

Poison

RW

0

Enables the Master Error Poison interrupt when bit is set.

31:29 Reserved

RO

0

Reserved

Table 2-13:

Interrupt Mask Register

(Cont’d)

Bits

Name

Core

Access

Reset

Value

Description

Table 2-14:

Bus Location Register

Bits

Name

Core

Access

Reset

Value

Description

2:0

Function Number

RO

0

Function number of the port for PCIe. Hard-wired to 0.

7:3

Device Number

RO

0

Device number of port for PCIe. For Endpoint, this register is RO

and is set by the Root Port.

15:8

Bus Number

RO

0

Bus number of port for PCIe. For Endpoint, this register is RO and

is set by the external Root Port.

23:16 Port Number

RW

0

Sets the Port number field of the Link Capabilities register.

31:24 Reserved

RO

0

Reserved