AXI Bridge for PCI Express v2.4

33

PG055 June 4, 2014

Chapter 2:

Product Specification

PHY Status/Control Register (Offset 0x144)

The PHY Status/Control register (described in

) provides the status of the current

PHY state, as well as control of speed and rate switching for Gen2-capable cores.

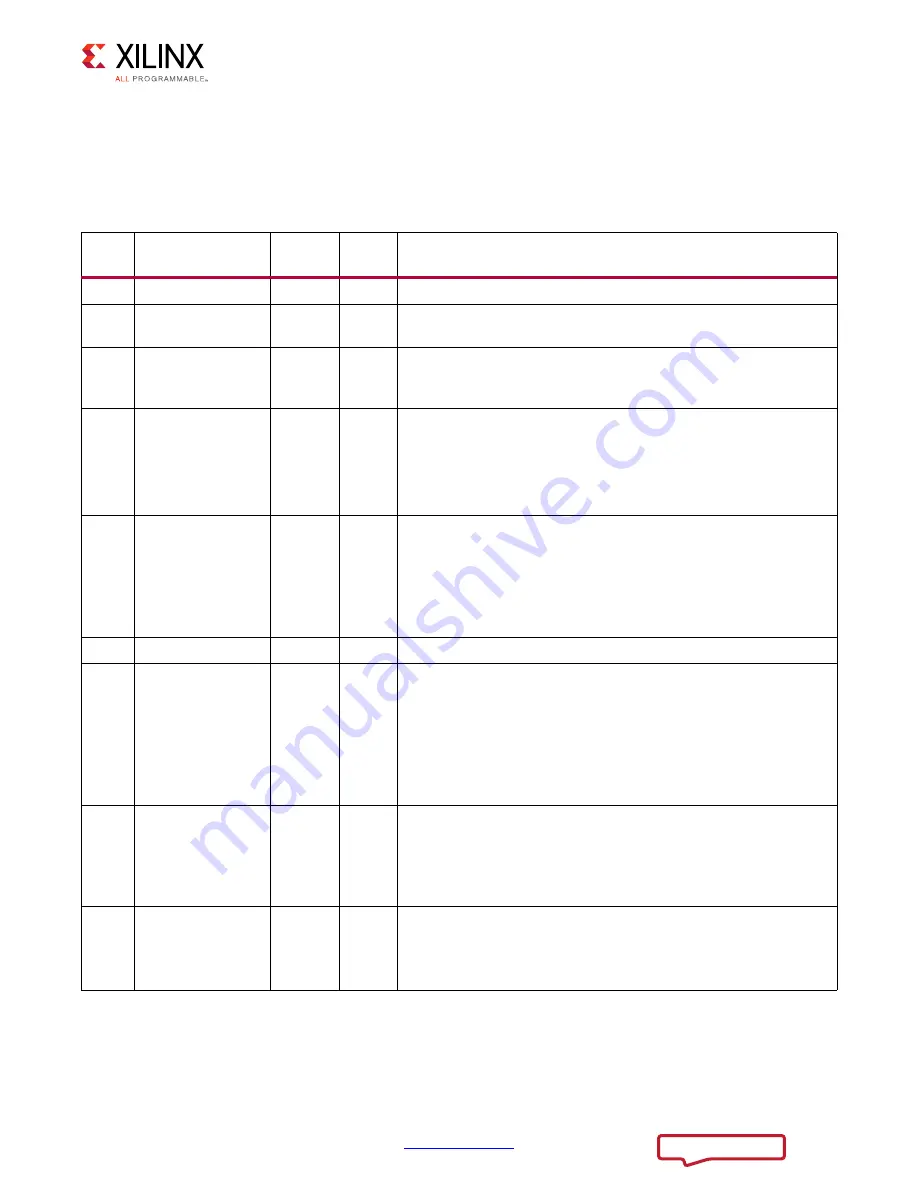

Table 2-15:

PHY Status/Control Register

Bits

Name

Core

Access

Reset

Value

Description

0

Link Rate

RO

0

Reports the current link rate. 0b = 2.5 GT/s, 1b = 5.0 GT/s.

2:1

Link Width

RO

0

Reports the current link width. 00b = x1, 01b = x2, 10b = x4, 11b

= x8.

8:3

LTSSM State

RO

0

Reports the current Link Training and Status State Machine

(LTSSM) state. Encoding is specific to the underlying integrated

block.

10:9

Lane Reversal

RO

0

Reports the current lane reversal mode.

• 00b: No reversal

• 01b: Lanes 1:0 reversed

• 10b: Lanes 3:0 reversed

• 11b: Lanes 7:0 reversed

11

Link Up

RO

0

Reports the current PHY Link-up state.

• 1b: Link up

• 0b: Link down

Link up indicates the core has achieved link up status, meaning

the LTSSM is in the L0 state and the core can send/receive data

packets.

15:12 Reserved

RO

0

Reserved

17:16 Directed Link

Width

RW

0

Specifies completer link width for a directed link change

operation. Only acted on when Directed Link Change specifies a

width change.

• 00b: x1

• 01b: x2

• 10b: x4

• 11b: x8

18

Directed Link

Speed

RW

0

Specifies completer link speed for a directed link change

operation. Only acted on when Directed Link Change specifies a

speed change.

• 0b: 2.5 GT/s

• 1b: 5.0 GT/s

19

Directed Link

Autonomous

RW

0

Specifies link reliability or autonomous for directed link change

operation.

• 0b: Link reliability

• 1b: Autonomous