Auxiliary Register Arithmetic Unit (ARAU)

3-13

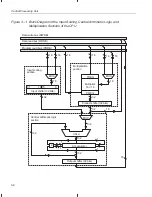

Central Processing Unit

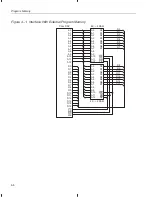

The eight auxiliary registers (AR7–AR0) provide flexible and powerful indirect

addressing. Any location in the 64K data memory space can be accessed us-

ing a 16-bit address contained in an auxiliary register. For the details of indirect

addressing, see Section 6.3 on page 6-9.

To select a specific auxiliary register, load the 3-bit auxiliary register pointer

(ARP) of status register ST0 with a value from 0 through 7. The ARP can be

loaded as a primary operation by the MAR instruction (which only performs

modifications to the auxiliary registers and the ARP) or by the LST instruction

(which can load a data-memory value to ST0 by way of the data read bus,

DRDB). The ARP can be loaded as a secondary operation by any instruction

that supports indirect addressing.

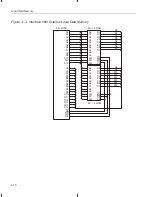

The register pointed to by the ARP is referred to as the

current auxiliary register

or

current AR. During the processing of an instruction, the content of the cur-

rent auxiliary register is used as the address at which the data-memory access

will take place. The ARAU passes this address to the data-read address bus

(DRAB) if the instruction requires a read from data memory, or it passes the

address to the data-write address bus (DWAB) if the instruction requires a

write to data memory. After the instruction uses the data value, the contents

of the current auxiliary register can be incremented or decremented by the

ARAU, which implements unsigned 16-bit arithmetic.

3.4.1

ARAU and Auxiliary Register Functions

The ARAU performs the following operations:

-

Increments or decrements an auxiliary register value by 1 or by an index

amount (by way of any instruction that supports indirect addressing)

-

Adds a constant value to an auxiliary register value (ADRK instruction) or

subtracts a constant value from an auxiliary register value (SBRK instruc-

tion). The constant is an 8-bit value taken from the eight LSBs of the

instruction word.

-

Compares the content of AR0 with the content of the current AR and puts

the result in the test/control flag bit (TC) of status register ST1 (CMPR

instruction). The result is passed to TC by way of the data write bus

(DWEB).

Normally, the ARAU performs its arithmetic operations in the decode phase of

the pipeline (when the instruction specifying the operations is being decoded).

This allows the address to be generated before the decode phase of the next

instruction. There is an exception to this rule: During processing of the NORM

instruction, the auxiliary register and/or ARP modification is done during the