On-Chip Peripherals

2-11

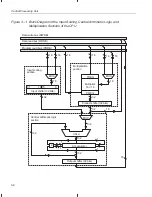

Architectural Overview

2.5

On-Chip Peripherals

All the ’C2xx devices have the same CPU, but different on-chip peripherals are

connected to their CPUs. The on-chip peripherals featured on the ’C2xx de-

vices are:

-

Clock generator (an oscillator and a phase lock loop circuit)

-

CLK register for turning the CLKOUT1 pin on and off

-

Timer

-

Wait-state generator

-

General-purpose input/output (I/O) pins

-

Synchronous serial port

-

Asynchronous serial port

2.5.1

Clock Generator

The clock generator consists of an internal oscillator and an internal phase lock

loop (PLL) circuit. The clock generator can be driven internally by connecting

the DSP to a crystal resonator circuit, or it can be driven by an external clock

source. The PLL circuit generates an internal CPU clock by multiplying the

clock source by a specified factor. Thus, you can use a clock source with a low-

er frequency than that of the CPU. The clock generator is discussed in Section

8.2, on page 8-4.

2.5.2

CLKOUT1-Pin Control (CLK) Register

The ’C2xx CLK register controls whether the master clock output signal

(CLKOUT1) is available at the CLKOUT1 pin.

2.5.3

Hardware Timer

The ’C2xx features a 16-bit down-counting timer with a 4-bit prescaler. Timer

control bits can stop, start, reload, and determine the prescaler count for the

timer. For more information, see Section 8.4,

Timer, on page 8-8.

2.5.4

Software-Programmable Wait-State Generator

Software-programmable wait-state logic is incorporated (without any external

hardware) for interfacing with slower off-chip memory and I/O devices. The

’C209 wait-state generator generates zero or one wait states; the wait-state

generator on other ’C2xx devices generates zero to seven wait states. For

more information, see Section 8.5,

Wait-State Generator, on page 8-14.