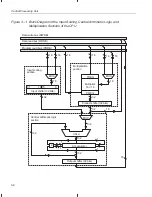

Central Processing Unit

2-5

Architectural Overview

2.2

Central Processing Unit

The CPU is the same on all the ’C2xx devices. The ’C2xx CPU contains:

-

A 32-bit central arithmetic logic unit (CALU)

-

A 32-bit accumulator

-

Input and output data-scaling shifters for the CALU

-

A 16-bit

×

16-bit multiplier

-

A product-scaling shifter

-

Data-address generation logic, which includes eight auxiliary registers

and an auxiliary register arithmetic unit (ARAU)

-

Program-address generation logic

2.2.1

Central Arithmetic Logic Unit (CALU) and Accumulator

The ’C2xx performs 2s-complement arithmetic using the 32-bit CALU. The

CALU uses 16-bit words taken from data memory or derived from an immedi-

ate instruction, or it uses the 32-bit result from the multiplier. In addition to arith-

metic operations, the CALU can perform Boolean operations.

The accumulator stores the output from the CALU; it can also provide a second

input to the CALU. The accumulator is 32 bits wide and is divided into a high-

order word (bits 31 through 16) and a low-order word (bits 15 through 0).

Assembly language instructions are provided for storing the high- and low-

order accumulator words to data memory.

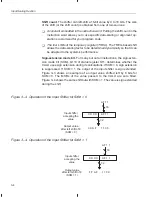

2.2.2

Scaling Shifters

The ’C2xx has three 32-bit shifters that allow for scaling, bit extraction, ex-

tended arithmetic, and overflow-prevention operations:

-

Input data-scaling shifter (input shifter). This shifter left shifts 16-bit in-

put data by 0 to 16 bits to align the data to the 32-bit input of the CALU.

-

Output data-scaling shifter (output shifter). This shifter can left shift

output from the accumulator by 0 to 7 bits before the output is stored to

data memory. The content of the accumulator remains unchanged.

-

Product-scaling shifter (product shifter). The product register (PREG)

receives the output of the multiplier. The product shifter shifts the output

of the PREG before that output is sent to the input of the CALU. The prod-

uct shifter has four product shift modes (no shift, left shift by one bit, left

shift by four bits, and right shift by 6 bits), which are useful for performing

multiply/accumulate operations, performing fractional arithmetic, or justi-

fying fractional products.