CHAPTER 15 SERIAL INTERFACE IICA

Page 507 of 920

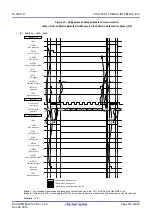

The following describes the operations in Figure 15 - 43 (4) Data ~ restart condition ~ address. After the operations

in steps <7> and <8>, the operations in steps <i> to <iii> are performed. These steps return the processing to step

<iii>, the data transmission step.

<7> After data transfer is completed, because of ACKEn = 1, the slave device sends an ACK by hardware to the

master device. The ACK is detected by the master device (ACKDn = 1) at the rising edge of the 9th clock.

<8> The master device and slave device set a wait status (SCLAn = 0) at the falling edge of the 9th clock, and both

the master device and slave device issue an interrupt (INTIICAn: end of transfer).

<i> The slave device reads the received data and releases the wait status (WRELn = 1).

<ii> The start condition trigger is set again by the master device (STTn = 1) and a start condition (i.e. SCLAn =1

changes SDAAn from 1 to 0) is generated once the bus clock line goes high (SCLAn = 1) and the bus data line

goes low (SDAAn = 0) after the restart condition setup time has elapsed. When the start condition is

subsequently detected, the master device is ready to communicate once the bus clock line goes low (SCLAn =

0) after the hold time has elapsed.

<iii> The master device writing the address + R/W (transmission) to the IICA shift register (IICAn) enables the slave

address to be transmitted.

Remark

n = 0, 1

Содержание RL78/G1H

Страница 941: ...R01UH0575EJ0120 RL78 G1H...