Configuring Interrupts

4

-18

DSP56303 User’s Manual

4.4

Configuring Interrupts

DSP56303 interrupt handling, like that for all DSP56300 family members, is optimized for

DSP applications. Refer to the sections describing interrupts in Chapter 2, Core Architecture

Overview, in the DSP56300 Family Manual. Two registers are used to configure the interrupt

characteristics:

n

Interrupt Priority Register-Core (IPRC)—Programmed to configure the priority levels

for the core DMA interrupts and the external interrupt lines as well as the interrupt line

trigger modes

n

Interrupt Priority Register-Peripherals (IPRP)—Programmed to configure the priority

levels for the interrupts used with the on-chip peripheral devices

The interrupt table resides in the 256 locations of program memory to which the PCU vector

base address (VBA) register points. These locations store the starting instructions of the

interrupt handler for each specified interrupt. The memory is programmed by the bootstrap

program at startup.

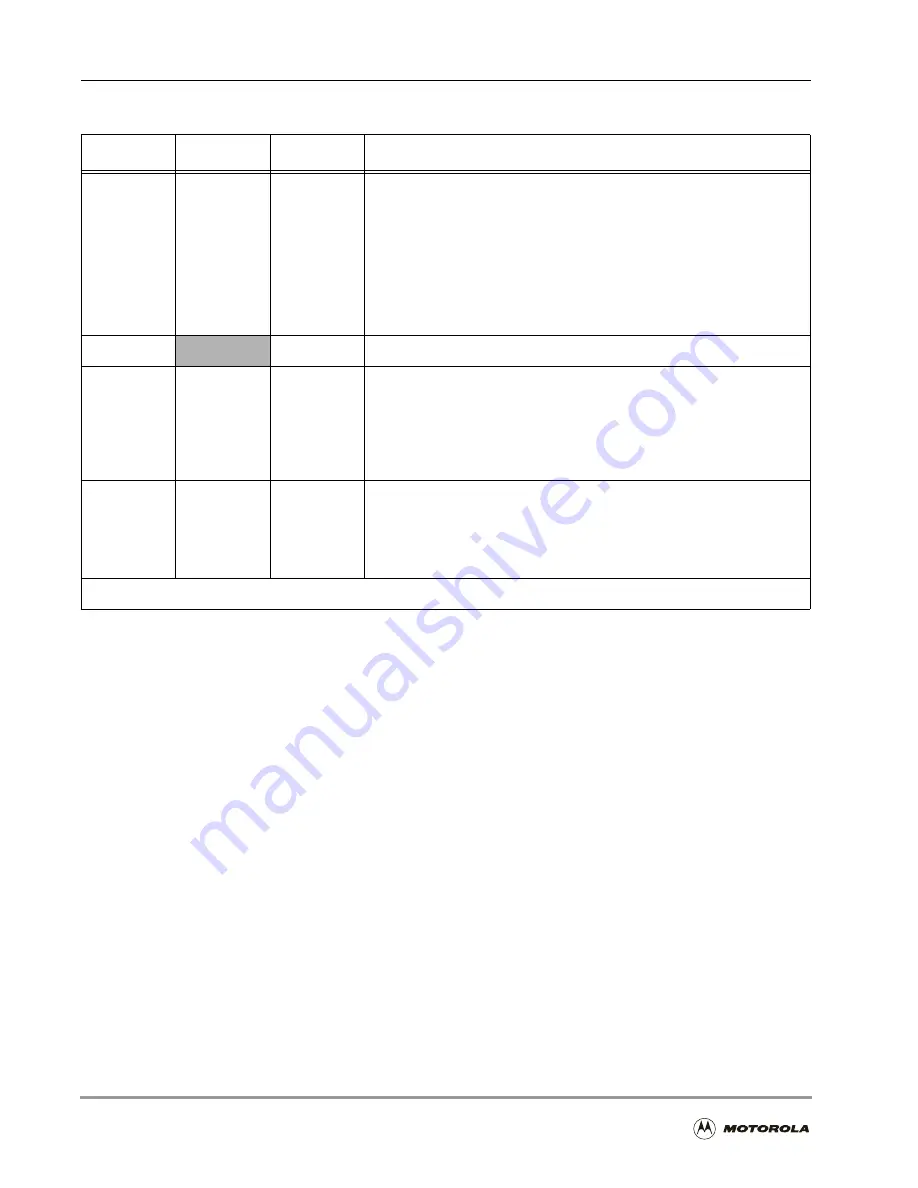

6

SD

0

Stop Delay Mode

Determines the length of the delay invoked when the core exits the Stop

state. The STOP instruction suspends core processing indefinitely until a

defined event occurs to restart it. If SD is cleared, a 128K clock cycle

delay is invoked before a STOP instruction cycle continues. However, if

SD is set, the delay before the instruction cycle continues is 16 clock

cycles. The long delay allows a clock stabilization period for the internal

clock to begin oscillating and to stabilize. When a stable external clock is

used, the shorter delay allows faster start-up of the DSP56300 core.

5

0

Reserved. Write to zero for future compatibility.

4

EBD

0

External Bus Disable

Disables the external bus controller to reduce power consumption when

external memories are not used. When EBD is set, the external bus

controller is disabled and external memory cannot be accessed. When

EBD is cleared, the external bus controller is enabled and external access

can be performed. Hardware reset clears the EBD bit.

3–0

MD–MA

*

Chip Operating Mode

Indicate the operating mode of the DSP56300 core. On hardware reset,

these bits are loaded from the external mode select pins, MODD, MODC,

MODB, and MODA, respectively. After the DSP56300 core leaves the

Reset state, MD–MA can be changed under program control.

* The MD–MA bits reflect the corresponding value of the mode input (that is, MODD–MODA), respectively.

Table 4-3. Operating Mode Register (OMR) Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description

Содержание DSP56303

Страница 1: ...DSP56303 User s Manual 24 Bit Digital Signal Processor DSP56303UM AD Revision 1 January 2001 ...

Страница 52: ...JTAG OnCE Interface 2 22 DSP56303 User s Manual ...

Страница 114: ...General Purpose Input Output GPIO 5 10 DSP56303 User s Manual ...

Страница 212: ...GPIO Signals and Registers 8 26 DSP56303 User s Manual ...

Страница 268: ...Interrupt Equates A 22 DSP56303 User s Manual ...

Страница 306: ...Programming Sheets B 38 DSP56303 User s Manual ...

Страница 320: ...Index 14 DSP56303 User s Manual ...