Operation

Host Interface (HI08)

6

-9

command interrupts, the interrupt acknowledge from the DSP56303 program controller clears

the pending interrupt condition.

Note:

When the DSP enters Stop mode, the HI08 pins are electrically disconnected

internally, thus disabling the HI08 until the core leaves Stop mode. Do not issue a

STOP command via the HI08 unless some other mechanism for exiting this mode

is provided.

6.4.3

Core DMA Access

The DSP56300 family Direct Memory Access (DMA) controller permits transfers between

internal or external memory and I/O without any core intervention. A DMA channel can be

set up to transfer data to/from the HTX and HRX data registers, freeing the core to use its

processing power on functions other than polling or interrupt routines for the HI08. DMA

may well be the best method to use for data transfers, but it requires that one of the six DMA

channels be available for use. Two HI08 DMA sources are possible, as Table 6-4 shows.

Refer to the DSP56300 Family Manual to learn about DMA accesses.

Note:

DMA transfers do not access the host bus. The host must determine when data is

available in the host-side data registers using an appropriate polling mechanism.

6.4.4

Host Requests

A set of signal lines allow the HI08 to request service from the host. The request signal lines

normally connect to the host interrupt request pins (IRQx) and indicate to the host when the

DSP HI08 port requires service. The HI08 can be configured to use either a single Host

Request (HREQ) line for both receive and transmit requests or two signal lines, a Host

Transmit Request (HTRQ) and a Host Receive Request (HRRQ), for each type of transfer.

Host requests are enabled on both the DSP-side and host-side. On the DSP side, the HPCR

Host Request Enable bit (HPCR[4]=HREN) is set to enable host requests. On the host side,

clearing the ICR Double Host Request bit (ICR[2]=HDRQ) configures the HI08 to use a

single request line (HREQ). Setting the ICR[2]=HDRQ bit enables both transmit and request

lines to be used. Further, the host uses the ICR Receive Request Enable bit (ICR[0]=RREQ)

and the ICR Transmit Request Enable bit (ICR[1]=TREQ) to enable receive and transmit

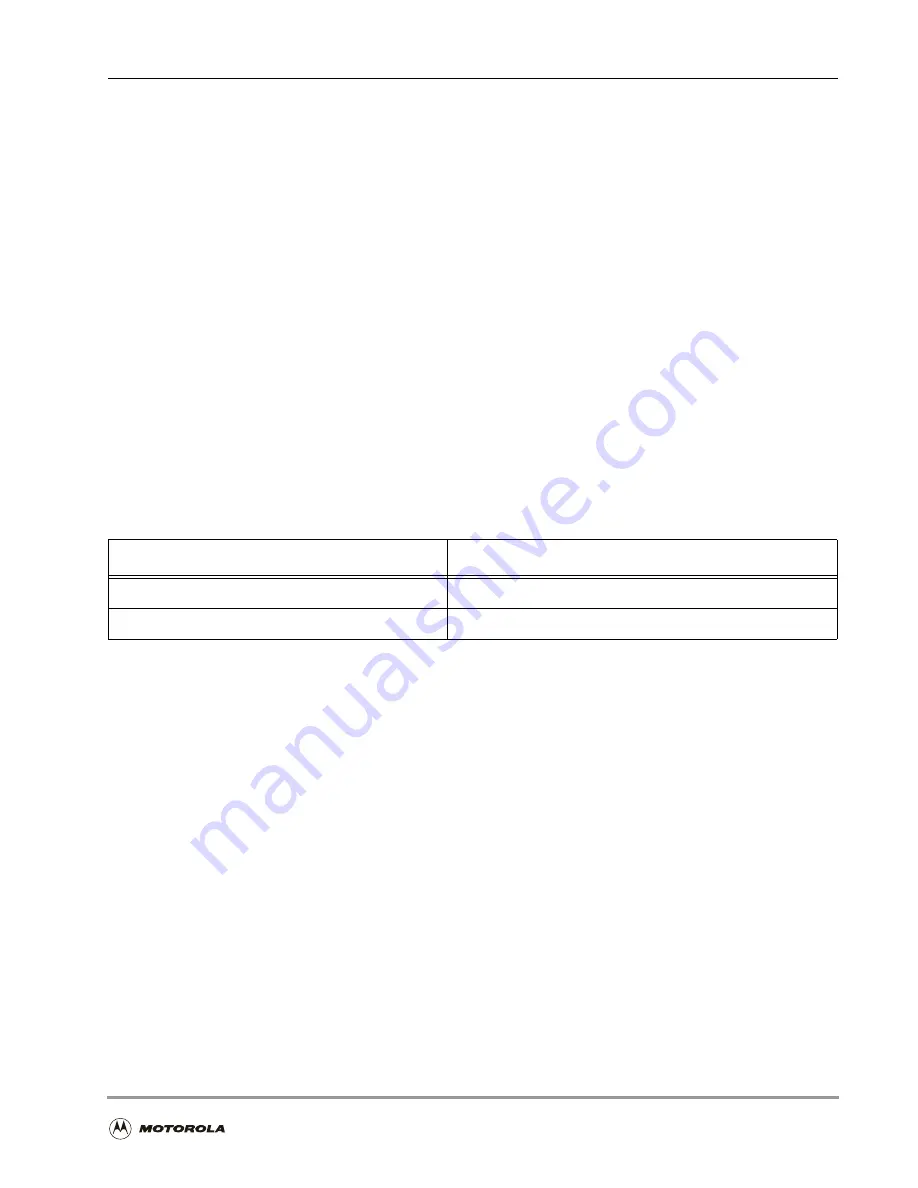

Table 6-4. DMA Request Sources

Requesting Device

DCRx[15–11]=DRS[4–0]

Host Receive Data Full (HRDF=1)

10011

Host Transmit Data Empty (HTDE=1)

10100

Содержание DSP56303

Страница 1: ...DSP56303 User s Manual 24 Bit Digital Signal Processor DSP56303UM AD Revision 1 January 2001 ...

Страница 52: ...JTAG OnCE Interface 2 22 DSP56303 User s Manual ...

Страница 114: ...General Purpose Input Output GPIO 5 10 DSP56303 User s Manual ...

Страница 212: ...GPIO Signals and Registers 8 26 DSP56303 User s Manual ...

Страница 268: ...Interrupt Equates A 22 DSP56303 User s Manual ...

Страница 306: ...Programming Sheets B 38 DSP56303 User s Manual ...

Страница 320: ...Index 14 DSP56303 User s Manual ...