Triple Timer Module Programming Model

9

-32

DSP56303 User’s Manual

2

TCIE

0

Timer Compare Interrupt Enable

Enables/disables the timer compare interrupts. When set, TCIE enables

the compare interrupts. In the timer, pulse width modulation (PWM), or

watchdog modes, a compare interrupt is generated after the counter value

matches the value of the TCPR. The counter starts counting up from the

number loaded from the TLR and if the TCPR value is M, an interrupt

occurs after (M – N + 1) events, where N is the value of TLR. When

cleared, the TCSR[TCIE] bit disables the compare interrupts.

1

TOIE

0

Timer Overflow Interrupt Enable

Enables timer overflow interrupts. When set, TOIE enables overflow

interrupt generation. The timer counter can hold a maximum value of

$FFFFFF. When the counter value is at the maximum value and a new

event causes the counter to be incremented to $000000, the timer

generates an overflow interrupt. When cleared, the TOIE bit disables

overflow interrupt generation.

0

TE

0

Timer Enable

Enables/disables the timer. When set, TE enables the timer and clears the

timer counter. The counter starts counting according to the mode selected

by the timer control (TC[3–0]) bit values. When clear, TE bit disables the

timer.

NOTE: When all three timers are disabled and the signals are not in GPIO

mode, all three TIO signals are tri-stated. To prevent undesired spikes on

the TIO signals when you switch from tri-state into active state, these

signals should be tied to the high or low signal state by pull-up or pull-down

resistors.

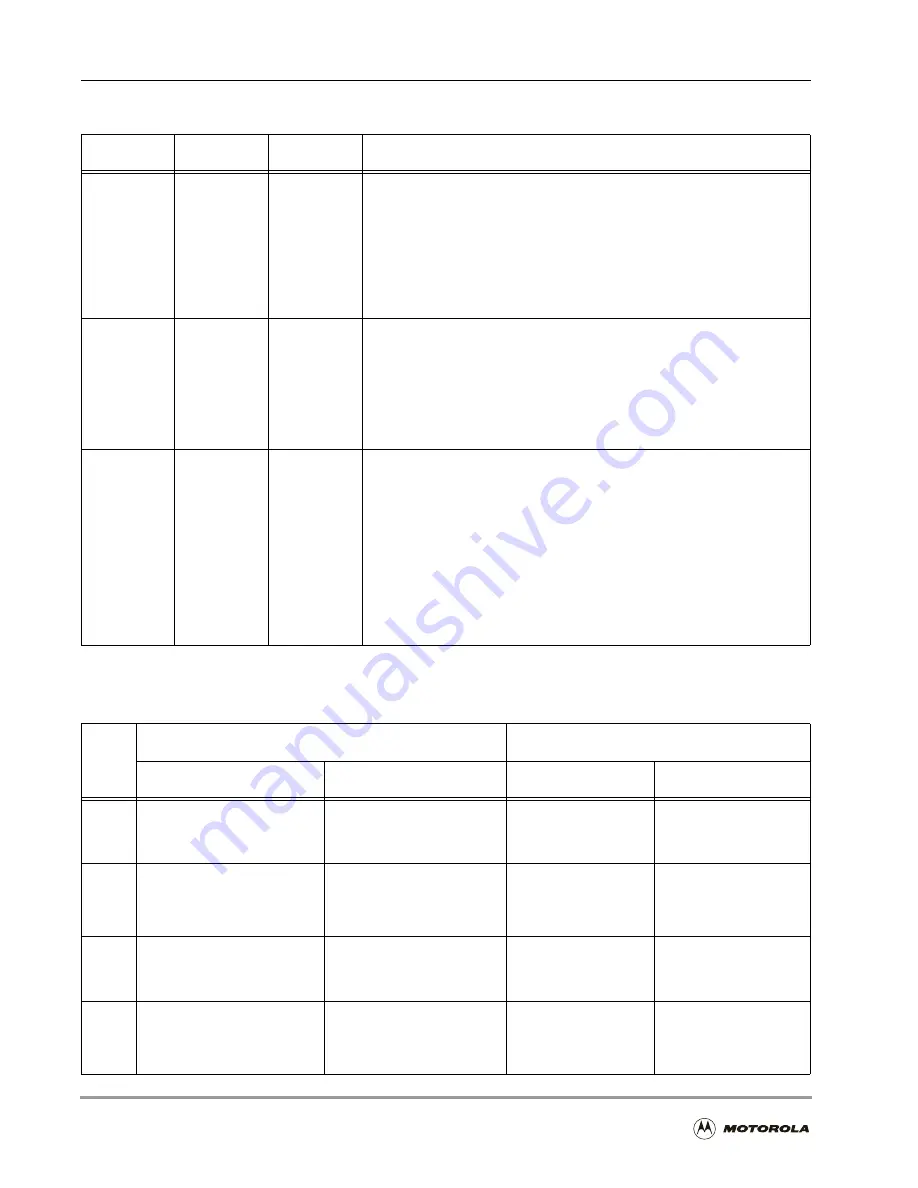

Table 9-4. Inverter (INV) Bit Operation

Mode

TIO Programmed as Input

TIO Programmed as Output

INV = 0

INV = 1

INV = 0

INV = 1

0

GPIO signal on the TIO

signal read directly.

GPIO signal on the TIO

signal inverted.

Bit written to GPIO

put on TIO signal

directly.

Bit written to GPIO

inverted and put on

TIO signal.

1

Counter is incremented on

the rising edge of the signal

from the TIO signal.

Counter is incremented on

the falling edge of the

signal from the TIO signal.

—

—

2

Counter is incremented on

the rising edge of the signal

from the TIO signal.

Counter is incremented on

the falling edge of the

signal from the TIO signal.

Initial output put on

TIO signal directly.

Initial output inverted

and put on TIO signal.

3

Counter is incremented on

the rising edge of the signal

from the TIO signal.

Counter is incremented on

the falling edge of the

signal from the TIO signal.

—

—

Table 9-3. Timer Control/Status Register (TCSR) Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description

Содержание DSP56303

Страница 1: ...DSP56303 User s Manual 24 Bit Digital Signal Processor DSP56303UM AD Revision 1 January 2001 ...

Страница 52: ...JTAG OnCE Interface 2 22 DSP56303 User s Manual ...

Страница 114: ...General Purpose Input Output GPIO 5 10 DSP56303 User s Manual ...

Страница 212: ...GPIO Signals and Registers 8 26 DSP56303 User s Manual ...

Страница 268: ...Interrupt Equates A 22 DSP56303 User s Manual ...

Страница 306: ...Programming Sheets B 38 DSP56303 User s Manual ...

Страница 320: ...Index 14 DSP56303 User s Manual ...