DSP56300 Core Functional Blocks

Overview

1

-9

1.5.5

JTAG TAP and OnCE Module

In the DSP56300 core is a dedicated user-accessible TAP that is fully compatible with the

IEEE 1149.1 Standard Test Access Port and Boundary Scan Architecture

.

Problems with

testing high-density circuit boards led to the development of this standard under the

sponsorship of the Test Technology Committee of IEEE and the JTAG. The DSP56300 core

implementation supports circuit-board test strategies based on this standard. The test logic

includes a TAP with four dedicated signals, a 16-state controller, and three test data registers.

A boundary scan register links all device signals into a single shift register. The test logic,

implemented utilizing static logic design, is independent of the device system logic. For

details on the JTAG port, consult the DSP56300 Family Manual.

The OnCE module interacts with the DSP56300 core and its peripherals nonintrusively so that

you can examine registers, memory, or on-chip peripherals. This facilitates hardware and

software development on the DSP56300 core processor. OnCE module functions are

provided through the JTAG TAP signals. For details on the OnCE module, consult the

DSP56300 Family Manual.

1.5.6

On-Chip Memory

The memory space of the DSP56300 core is partitioned into program, X data, and Y data

memory space. The data memory space is divided into X and Y data memory in order to work

with the two address ALUs and to feed two operands simultaneously to the data ALU.

Memory space includes internal RAM and ROM and can be expanded off-chip under

software control. For details on internal memory, see Chapter 3,

Memory Configuration.

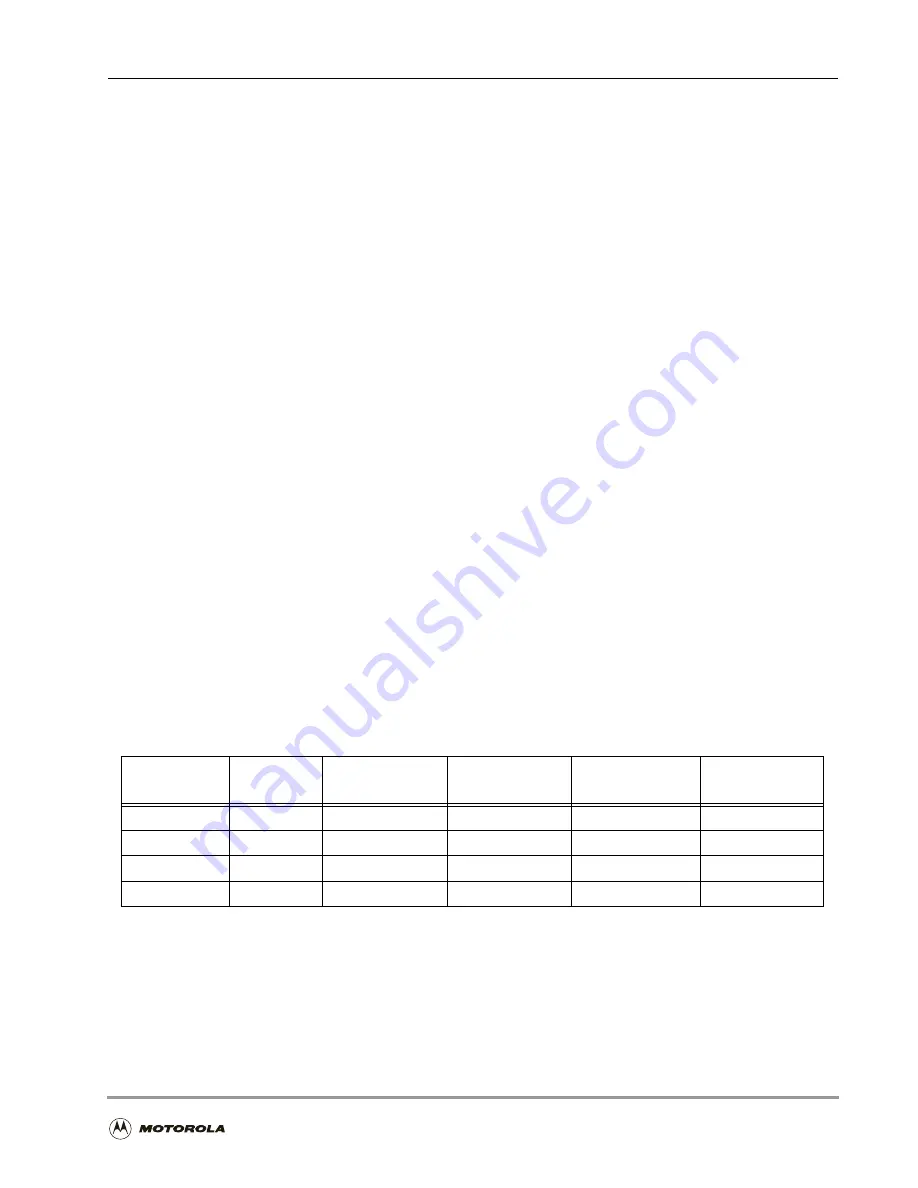

Program RAM, instruction cache, X data RAM, and Y data RAM size are programmable, as

shown in Table 1-2.

There is an on-chip 192 x 24-bit bootstrap ROM.

Table 1-2. On-Chip Memory

Instruction

Cache

Switch

Mode

Program RAM

Size

Instruction

Cache Size

X Data RAM Size

Y Data RAM Size

disabled

disabled

4096

×

24-bit

0

2048

×

24-bit

2048

×

24-bit

enabled

disabled

3072

×

24-bit

1024

×

24-bit

2048

×

24-bit

2048

×

24-bit

disabled

enabled

2048

×

24-bit

0

3072

×

24-bit

3072

×

24-bit

enabled

enabled

1024

×

24-bit

1024

×

24-bit

3072

×

24-bit

3072

×

24-bit

Содержание DSP56303

Страница 1: ...DSP56303 User s Manual 24 Bit Digital Signal Processor DSP56303UM AD Revision 1 January 2001 ...

Страница 52: ...JTAG OnCE Interface 2 22 DSP56303 User s Manual ...

Страница 114: ...General Purpose Input Output GPIO 5 10 DSP56303 User s Manual ...

Страница 212: ...GPIO Signals and Registers 8 26 DSP56303 User s Manual ...

Страница 268: ...Interrupt Equates A 22 DSP56303 User s Manual ...

Страница 306: ...Programming Sheets B 38 DSP56303 User s Manual ...

Страница 320: ...Index 14 DSP56303 User s Manual ...