Programming Model Quick Reference

6

-34

DSP56303 User’s Manual

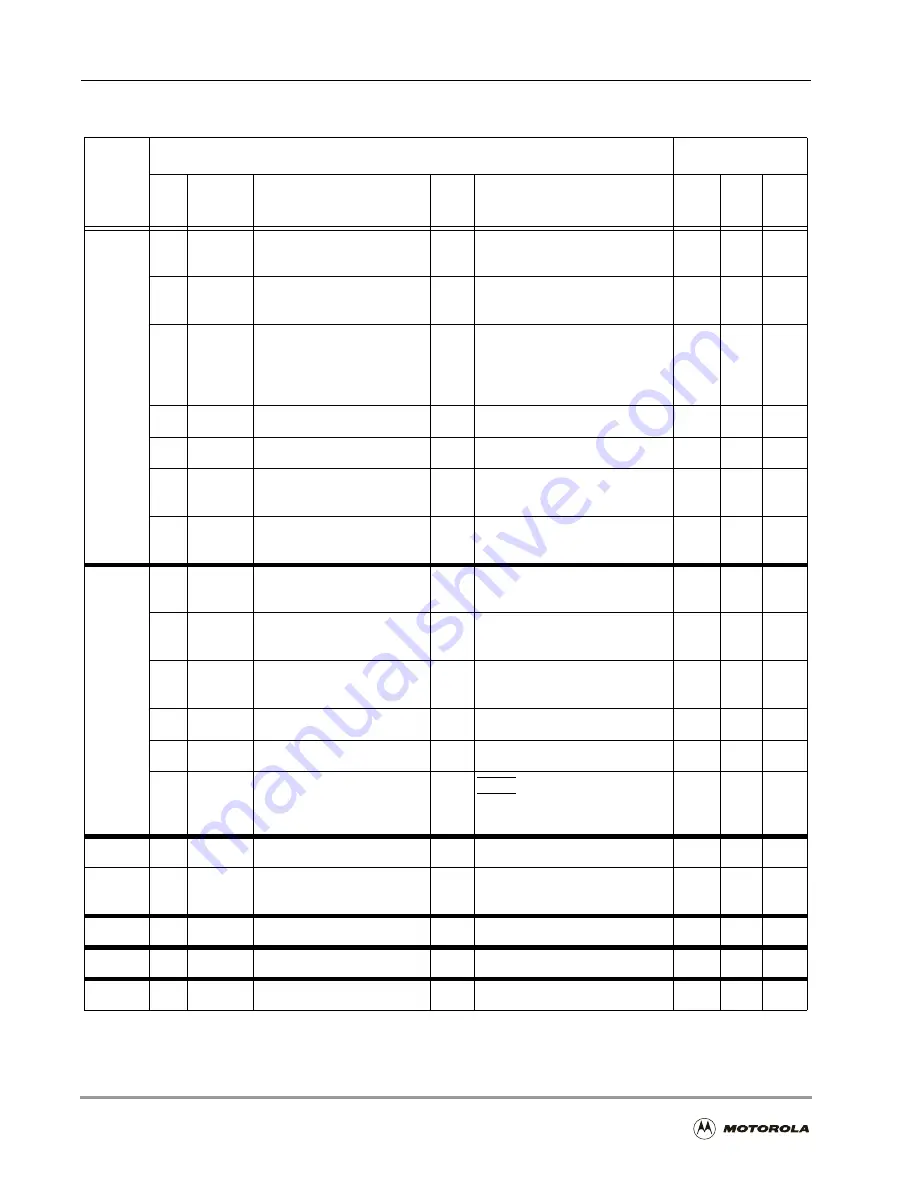

Table 6-20. HI08 Programming Model: Host Side

Reg

Bit

Reset Type

#

Name

Value

Function

HW/

SW

Indivi

-dual

STOP

ICR

0

RREQ

Receive Request Enable

0

1

HRRQ interrupt disabled

HRRQ interrupt enabled

0

—

—

1

TREQ

Transmit Request Enable

0

1

HTRQ interrupt disabled

HTRQ interrupt enabled

0

—

—

2

HDRQ

Double Host Request

0

1

HREQ/HTRQ = HREQ,

HACK/HRRQ = HACK

HREQ/HTRQ = HTRQ,

HACK/HRRQ = HRRQ

0

—

—

3

HF0

Host Flag 0

0

—

—

4

HF1

Host Flag 1

0

—

—

5

HLEND

Host Little Endian

0

1

Big Endian order

Little Endian order

0

—

—

7

INIT

Initialize

1

Reset data paths according to

TREQ and RREQ

0

—

—

ISR

0

RXDF

Receive Data Register Full

0

1

Host Receive Register is empty

Host Receive Register is full

0

0

0

1

TXDE

Transmit Data Register

Empty

1

0

Host Transmit Register is empty

Host Transmit Register is full

1

1

1

2

TRDY

Transmitter Ready

1

0

transmit FIFO (6 deep) is empty

transmit FIFO is not empty

1

1

1

3

HF2

Host Flag 2

0

—

—

4

HF3

Host Flag 3

0

—

—

7

HREQ

Host Request

0

1

HREQ signal is deasserted

HREQ signal is asserted (if

enabled)

0

0

0

CVR

6–0

HV[6–0] Host Command Vector

$32

—

—

CVR

7

HC

Host Command

0

1

no host command pending

host command pending

0

0

0

RXH/M/L

7–0

Host Receive Data Register

empty

TXH/M/L

7–0

Host Transmit Data Register

empty

IVR

7–0

IV[7–0]

Interrupt Register

68000 family vector register

$0F

—

—

Содержание DSP56303

Страница 1: ...DSP56303 User s Manual 24 Bit Digital Signal Processor DSP56303UM AD Revision 1 January 2001 ...

Страница 52: ...JTAG OnCE Interface 2 22 DSP56303 User s Manual ...

Страница 114: ...General Purpose Input Output GPIO 5 10 DSP56303 User s Manual ...

Страница 212: ...GPIO Signals and Registers 8 26 DSP56303 User s Manual ...

Страница 268: ...Interrupt Equates A 22 DSP56303 User s Manual ...

Страница 306: ...Programming Sheets B 38 DSP56303 User s Manual ...

Страница 320: ...Index 14 DSP56303 User s Manual ...