Host Programmer Model

6

-28

DSP56303 User’s Manual

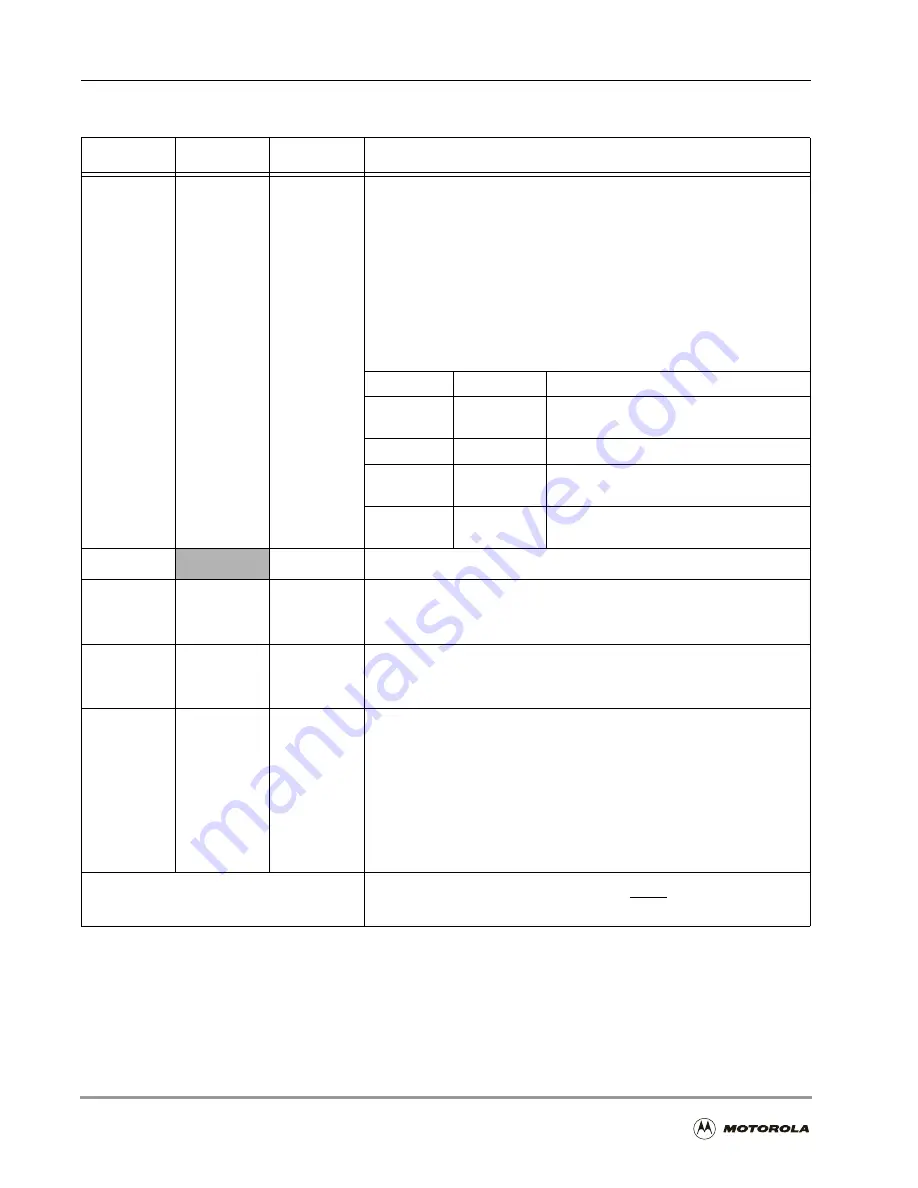

Table 6-17. Interface Status Register (ISR) Bit Definitions

Bit Number

Bit Name

Reset Value

Description

7

HREQ

0 (Hardware

and Software

reset)

1 (Individual

reset and

TREQ is set)

1 (Stop reset

and TREQ is

set)

Host Request

If HDRQ is set, the HREQ bit indicates the status of the external transmit

and receive request output signals (HTRQ and HRRQ). If HDRQ is

cleared, HREQ indicates the status of the external host request output

signal (HREQ). The HREQ bit is set from either or both of two conditions—

the receive byte registers are full or the transmit byte registers are empty.

These conditions are indicated by status bits: ISR RXDF indicates that the

receive byte registers are full, and ISR TXDE indicates that the transmit

byte registers are empty. If the interrupt source is enabled by the

associated request enable bit in the ICR, HREQ is set if one or more of the

two enabled interrupt sources is set.

HDRQ

HREQ

Effect

0

0

HREQ is cleared; no host processor

interrupts are requested.

0

1

HREQ is set; an interrupt is requested.

1

0

HTRQ and HRRQ are cleared, no host

processor interrupts are requested.

1

1

HTRQ or HRRQ are set; an interrupt is

requested.

6–5

0

Reserved. Write to 0 for future compatibility.

4

HF3

0

Host Flag 3

Indicates the state of HF3 in the HCR on the DSP side. HF3 can be

changed only by the DSP56303. Hardware and software reset clear HF3.

3

HF2

0

Host Flag 2

Indicates the state of HF2 in the HCR on the DSP side. HF2 can be

changed only by the DSP56303. Hardware and software reset clear HF2.

2

TRDY

1

Transmitter Ready

Indicates that TXH:TXM:TXL and the HRX registers are empty. If TRDY is

set, the data that the host processor writes to TXH:TXM:TXL is

immediately transferred to the DSP side of the HI08. This feature has

many applications. For example, if the host processor issues a host

command that causes the DSP56303 to read the HRX, the host processor

can be guaranteed that the data it just transferred to the HI08 is that being

received by the DSP56303. Hardware, software, individual, and stop

resets all set TRDY.

CAUTION:

TRDY = TXDE and HRDF

Содержание DSP56303

Страница 1: ...DSP56303 User s Manual 24 Bit Digital Signal Processor DSP56303UM AD Revision 1 January 2001 ...

Страница 52: ...JTAG OnCE Interface 2 22 DSP56303 User s Manual ...

Страница 114: ...General Purpose Input Output GPIO 5 10 DSP56303 User s Manual ...

Страница 212: ...GPIO Signals and Registers 8 26 DSP56303 User s Manual ...

Страница 268: ...Interrupt Equates A 22 DSP56303 User s Manual ...

Страница 306: ...Programming Sheets B 38 DSP56303 User s Manual ...

Страница 320: ...Index 14 DSP56303 User s Manual ...