System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-18

ID021414

Non-Confidential

Configurations

ID_PFR0_EL1 is architecturally mapped to AArch32 register ID_PFR0.

See

Processor Feature Register 0

on page 4-160

.

Attributes

ID_PFR0_EL1 is a 32-bit register.

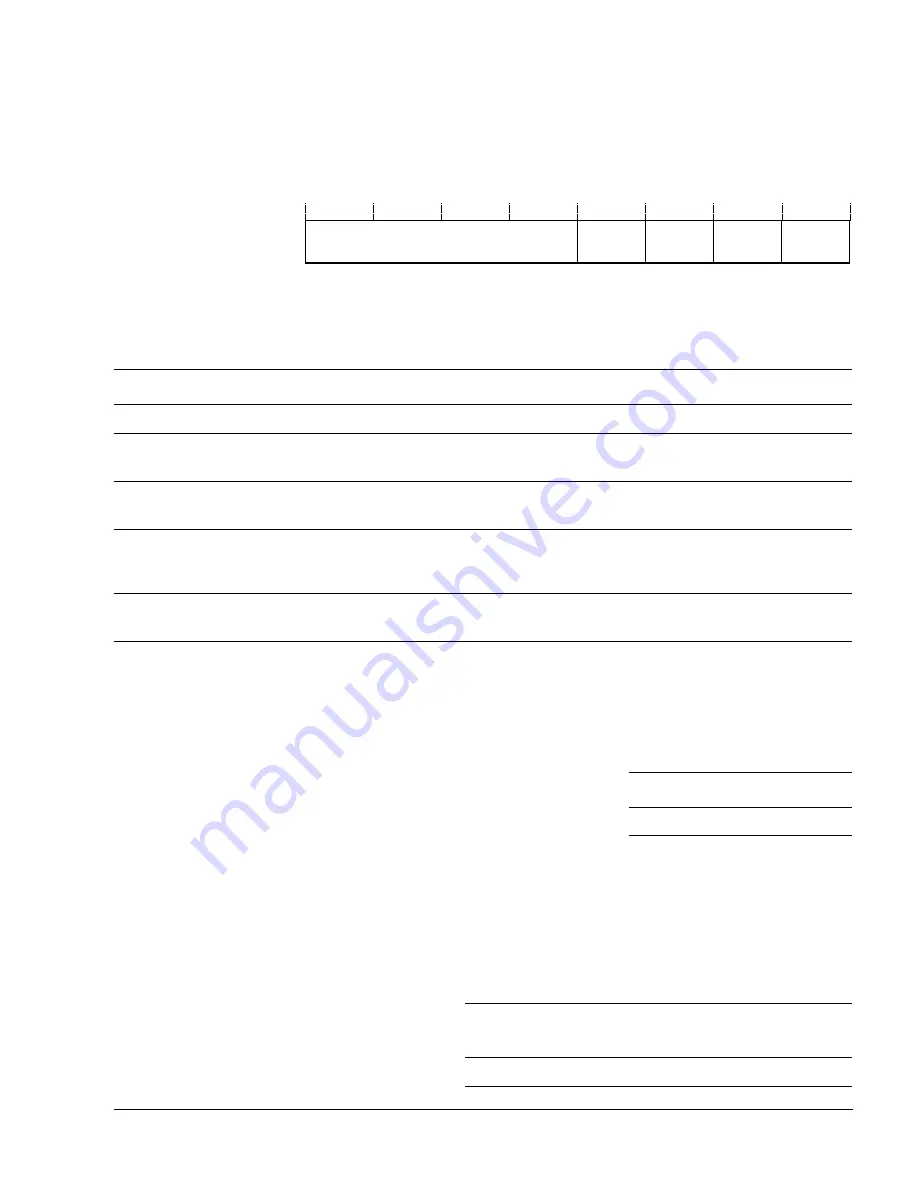

Figure 4-4

shows the ID_PFR0_EL1 bit assignments.

Figure 4-4 ID_PFR0_EL1 bit assignments

Table 4-19

shows the ID_PFR0_EL1 bit assignments.

To access the ID_PFR0_EL1:

MRS <Xt>, ID_PFR0_EL1 ; Read ID_PFR0_EL1 into Xt

Register access is encoded as follows:

4.3.5

AArch32 Processor Feature Register 1

The ID_PFR1_EL1 characteristics are:

Purpose

Provides information about the programmers model and architecture

extensions supported by the processor.

Usage constraints

This register is accessible as follows:

31

12 11

8 7

0

RES

0

State2

State1

16 15

4 3

State0

State3

Table 4-19 ID_PFR0_EL1 bit assignments

Bits

Name

Function

[31:16]

-

Reserved,

RES

0.

[15:12]

State3

Indicates support for

Thumb Execution Environment

(T32EE) instruction set. This value is:

0x0

Processor does not support the T32EE instruction set.

[11:8]

State2

Indicates support for Jazelle. This value is:

0x1

Processor supports trivial implementation of Jazelle.

[7:4]

State1

Indicates support for T32 instruction set. This value is:

0x3

Processor supports T32 encoding after the introduction of Thumb-2 technology, and for all 16-bit

and 32-bit T32 basic instructions.

[3:0]

State0

Indicates support for A32 instruction set. This value is:

0x1

A32 instruction set implemented.

Table 4-20 REVIDR access encoding

op0

op1

CRn

CRm

op2

1111

000

0000

0001

000

EL0

EL1

(NS)

EL1

(S)

EL2

EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

RO

RO

RO

RO

RO