System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-164

ID021414

Non-Confidential

Attributes

ID_DFR0 is a 32-bit register.

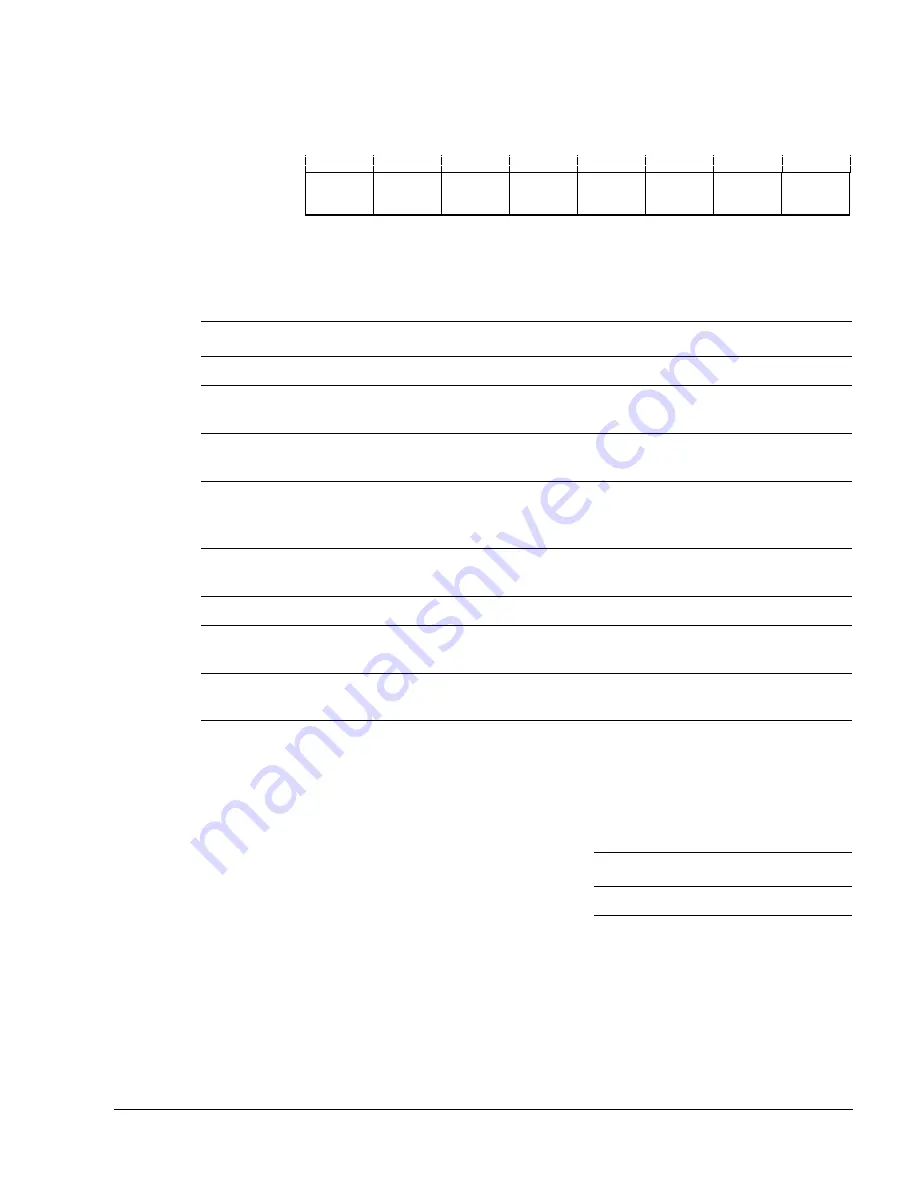

Figure 4-81

shows the ID_DFR0 bit assignments.

Figure 4-81 ID_DFR0 bit assignments

Table 4-158

shows the ID_DFR0 bit assignments.

To access the ID_DFR0:

MRC p15,0,<Rt>,c0,c1,2 ; Read ID_DFR0 into Rt

Register access is encoded as follows:

4.5.9

Auxiliary Feature Register 0

This register is always

RES

0.

31

12 11

8 7

0

RES

0

4 3

24 23

20 19

16 15

28 27

PerfMon

MProfDbg

MMapTrc

CopTrc

CopSDbg

CopDbg

Reserved

Table 4-158 ID_DFR0 bit assignments

Bits

Name

Function

[31:28]

-

Reserved,

RES

0.

[27:24]

PerfMon

Indicates support for performance monitor model:

0x3

Support for

Performance Monitor Unit version 3

(PMUv3) system registers.

[23:20]

MProfDbg

Indicates support for memory-mapped debug model for M profile processors:

0x0

Processor does not support M profile Debug architecture.

[19:16]

MMapTrc

Indicates support for memory-mapped trace model:

0x1

Support for ARM trace architecture, with memory-mapped access.

In the Trace registers, the ETMIDR gives more information about the implementation.

[15:12]

CopTrc

Indicates support for coprocessor-based trace model:

0x0

Processor does not support ARM trace architecture, with CP14 access.

[11:8]

-

Reserved, RAZ.

[7:4]

CopSDbg

Indicates support for coprocessor-based Secure debug model:

0x6

Processor supports v8 Debug architecture, with CP14 access.

[3:0]

CopDbg

Indicates support for coprocessor-based debug model:

0x6

Processor supports v8 Debug architecture, with CP14 access.

Table 4-159 ID_DFR0 access encoding

coproc

opc1

CRn

CRm

opc2

1111

000

0000

0001

010