Functional Description

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

2-16

ID021414

Non-Confidential

2.4

Power management

The Cortex-A53 processor provides mechanisms and support to control both dynamic and static

power dissipation. The individual cores in the Cortex-A53 processor support four main levels

of power management. This section describes:

•

Power domains

.

•

Power modes

on page 2-17

.

•

Event communication using WFE or SEV

on page 2-25

.

•

Communication to the Power Management Controller

on page 2-26

.

2.4.1

Power domains

Table 2-2

shows the power domains that the Cortex-A53 processor supports:

The separate PDCORTEXA53 and PDL2 power domains can remain active even when all the

cores are powered down. This means the Cortex-A53 processor can continue to accept snoops

from external devices to access the L2 cache.

Figure 2-8 on page 2-17

shows an example of the domains embedded in a

System-on-Chip

(SoC) power domain.

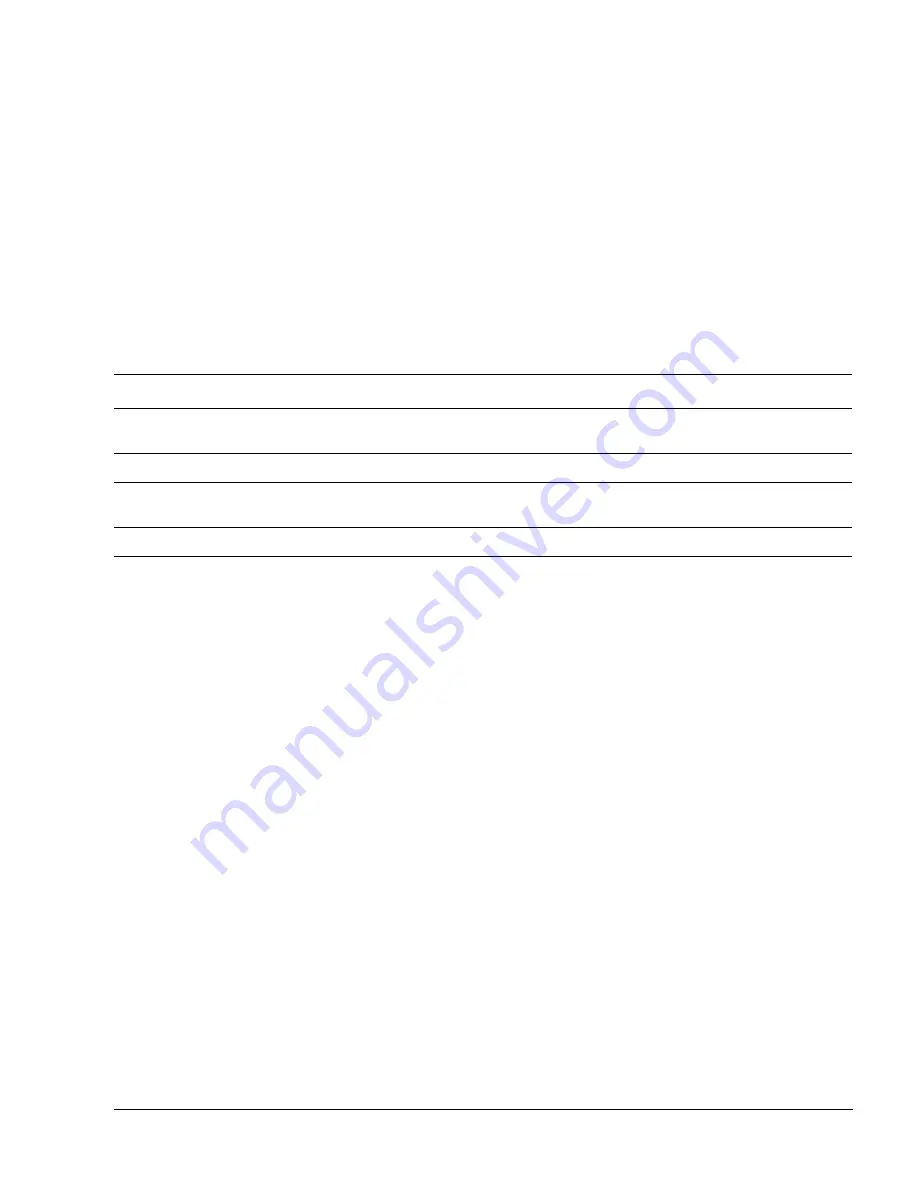

Table 2-2 Power domain description

Power domain

Description

PDCORTEXA53

This includes the SCU, the optional L2 cache controller, and debug registers described as being in the

debug domain.

PDL2

This includes the L2 data RAM, L2 tag RAM, L2 victim RAM, and the SCU duplicate tag RAM.

PDCPU<n

a

>

This includes the optional Advanced SIMD and Floating-point Extension, the L1 TLB, L1 processor

RAMs, and debug registers described as being in the processor domain.

PDCPUADVSIMD<n

a

>

This represents the Advanced SIMD and Floating-point block of core n.

a. <n> where n is 0, 1, 2, or 3. This represents core 0, core 1, core 2, or core 3. If a core is not present, the corresponding Power Domain is not

present.