System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-153

ID021414

Non-Confidential

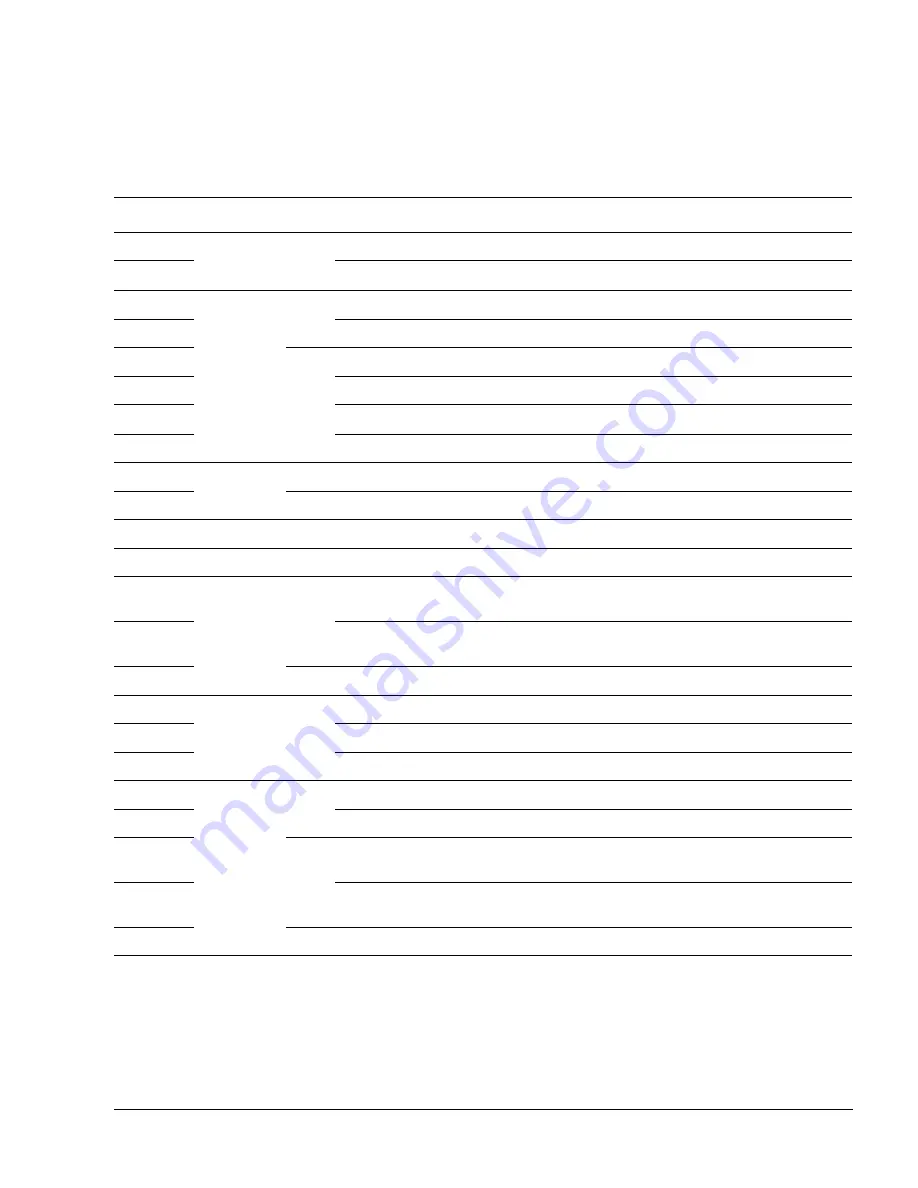

4.4.25

AArch32 Virtualization registers

Table 4-145

shows the Virtualization registers. See the

ARM

®

Architecture Reference Manual

ARMv8, for ARMv8-A architecture profile

for more information.

Table 4-145 Virtualization registers

Name

CRn

Op1

CRm

Op2

Reset

Width

Description

VPIDR

c0

4

c0

0

0x410FD032

32-bit

Virtualization Processor ID Register

on page 4-189

VMPIDR

5

-

a

32-bit

Virtualization Multiprocessor ID Register

on page 4-190

HSCTLR

c1

4

c0

0

0x30C50838

32-bit

Hyp System Control Register

on page 4-207

HACTLR

1

UNK

Hyp Auxiliary Control Register

on page 4-205

HCR

c1

0

0x00000000

32-bit

Hyp Configuration Register

HDCR

1

0x00000006

32-bit

Hyp Debug Control Register

on page 4-217

HCPTR

2

0x000033FF

b

32-bit

Hyp Architectural Feature Trap Register

on page 4-221

HSTR

3

0x00000000

32-bit

Hypervisor System Trap Register

HTCR

c2

4

c0

2

UNK

32-bit

Hyp Translation Control Register

on page 4-232

VTCR

c1

2

UNK

32-bit

Virtualization Translation Control Register

HTTBR

-

4

c2

-

UNK

64-bit

Hyp Translation Table Base Register

VTTBR

-

6

c2

-

UNK

64-bit

Virtualization Translation Table Base Register

HADFSR

c5

4

c1

0

0x00000000

32-bit

Hyp Auxiliary Data Fault Status Syndrome Register

on

page 4-246

HAIFSR

1

0x00000000

32-bit

Hyp Auxiliary Instruction Fault Status Syndrome Register

on page 4-246

HSR

c2

0

UNK

32-bit

Hyp Syndrome Register

on page 4-246

HDFAR

c6

4

c0

0

UNK

32-bit

Hyp Data Fault Address Register

HIFAR

2

UNK

32-bit

Hyp Instruction Fault Address Register

HPFAR

4

UNK

32-bit

Hyp IPA Fault Address Register

HMAIR0

c10

4

c2

0

UNK

32-bit

Hyp Memory Attribute Indirection Register 0

HMAIR1

1

UNK

32-bit

Hyp Memory Attribute Indirection Register 1

HAMAIR0

c3

0

0x00000000

32-bit

Hyp Auxiliary Memory Attribute Indirection Register 0

on

page 4-263

HAMAIR1

1

0x00000000

32-bit

Hyp Auxiliary Memory Attribute Indirection Register 1

on

page 4-263

HVBAR

c12

4

c0

0

UNK

32-bit

Hyp Vector Base Address Register

a. The reset value is the value of the Multiprocessor Affinity Register.

b. The reset value depends on the FPU and NEON configuration. If Advanced SIMD and Floating-point are implemented, the reset value is

0x000033FF

. If Advanced SIMD and Floating-point are not implemented, the reset value is

0x0000BFFF

.