System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-138

ID021414

Non-Confidential

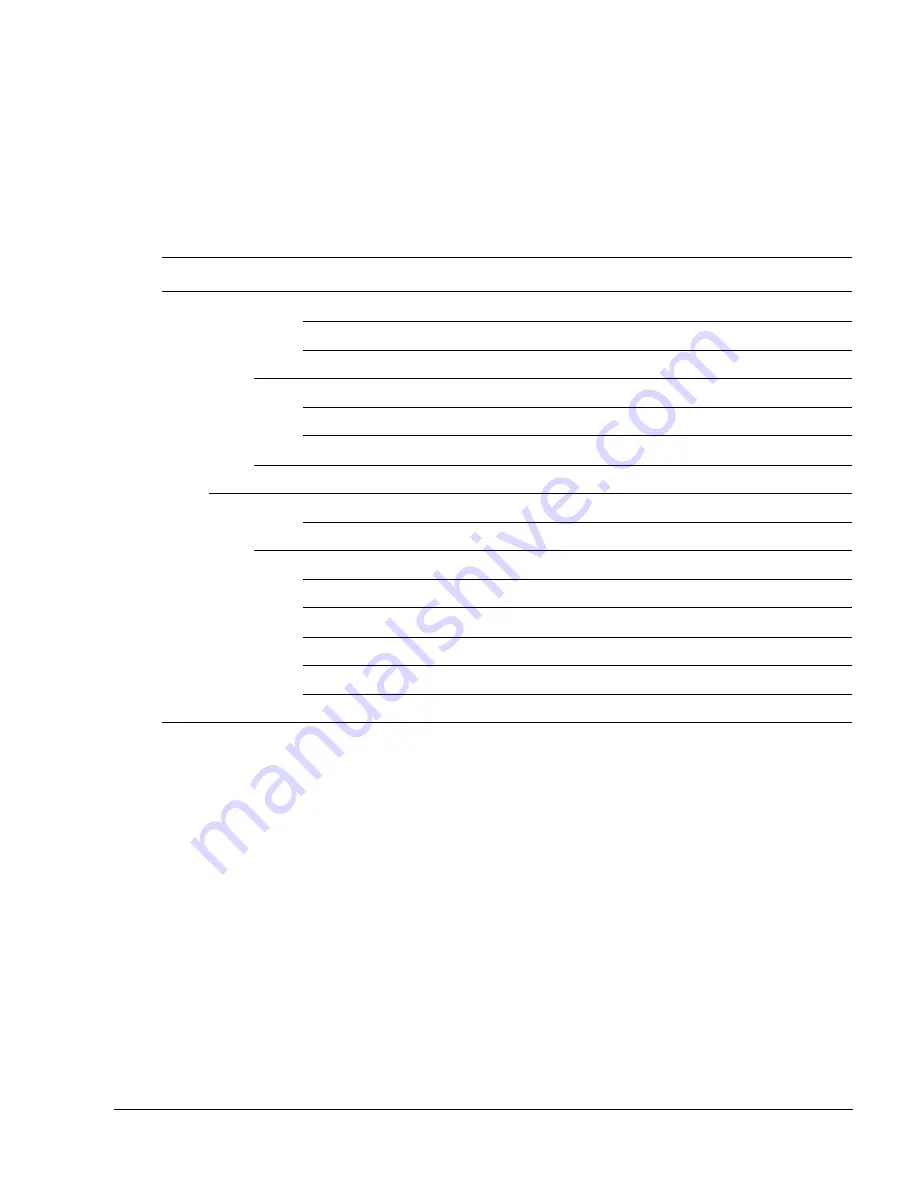

4.4.2

c1 registers

Table 4-123

shows the 32-bit wide system registers you can access when the processor is in

AArch32 state and the value of CRn is c1.

d. The value is

0x09200003

if the L2 cache is not implemented.

e. The reset value is the value of the Multiprocessor Affinity Register.

Table 4-123 c1 register summary

CRn

Op1

CRm

Op2

Name

Reset

Description

c1

0

c0

0

SCTLR

0x00C50838

a

System Control Register

on page 4-191

1

ACTLR

0x00000000

Auxiliary Control Register

on page 4-196

2

CPACR

0x00000000

Architectural Feature Access Control Register

on page 4-197

c1

0

SCR

0x00000000

Secure Configuration Register

on page 4-199

1

SDER

0x00000000

Secure Debug Enable Register

on page 4-201

2

NSACR

0x00000000

b

Non-Secure Access Control Register

on page 4-202

c3

1

SDCR

0x00000000

Secure Debug Control Register

on page 4-204

4

c0

0

HSCTLR

0x03C50838

Hyp System Control Register

on page 4-207

1

HACTLR

0x00000000

Auxiliary Control Register, EL2

on page 4-55

c1

0

HCR

0x00000000

Hyp Configuration Register

on page 4-211

1

HDCR

0x00000006

Hyp Debug Control Register

on page 4-217

2

HCPTR

0x000033FF

c

Hyp Architectural Feature Trap Register

on page 4-221

3

HSTR

0x00000000

Hyp System Trap Register

on page 4-236

4

HCR2

0x00000000

Hyp Configuration Register 2

on page 4-216

7

HACR

0x00000000

Hyp Architectural Feature Trap Register

on page 4-221

a. The reset value depends on inputs,

CFGTE

,

CFGEND

, and

VINITHI

. The value shown in

Table 4-122 on page 4-137

assumes

these signals are set to LOW.

b. If EL3 is AArch64 then the NSACR reads as

0x00000C00

.

c. The reset value depends on the FPU and NEON configuration. If Advanced SIMD and Floating-point are implemented, the reset

value is

0x000033FF

. If Advanced SIMD and Floating-point are not implemented, the reset value is

0x0000BFFF

.