Debug

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

11-18

ID021414

Non-Confidential

To access the DBGDIDR in AArch32 Execution state, read the CP14 register with:

MRC p14, 0, <Rt>, c0, c0, 0; Read Debug ID Register

11.6.2

Debug Device ID Register

The DBGDEVID characteristics are:

Purpose

Specifies the version of the Debug architecture is implemented, and some

features of the debug implementation.

Usage constraints

This register is accessible as follows:

Configurations

There is one copy of this register that is used in both Secure and

Non-secure states.

Attributes

See the register summary in

Table 11-7 on page 11-15

.

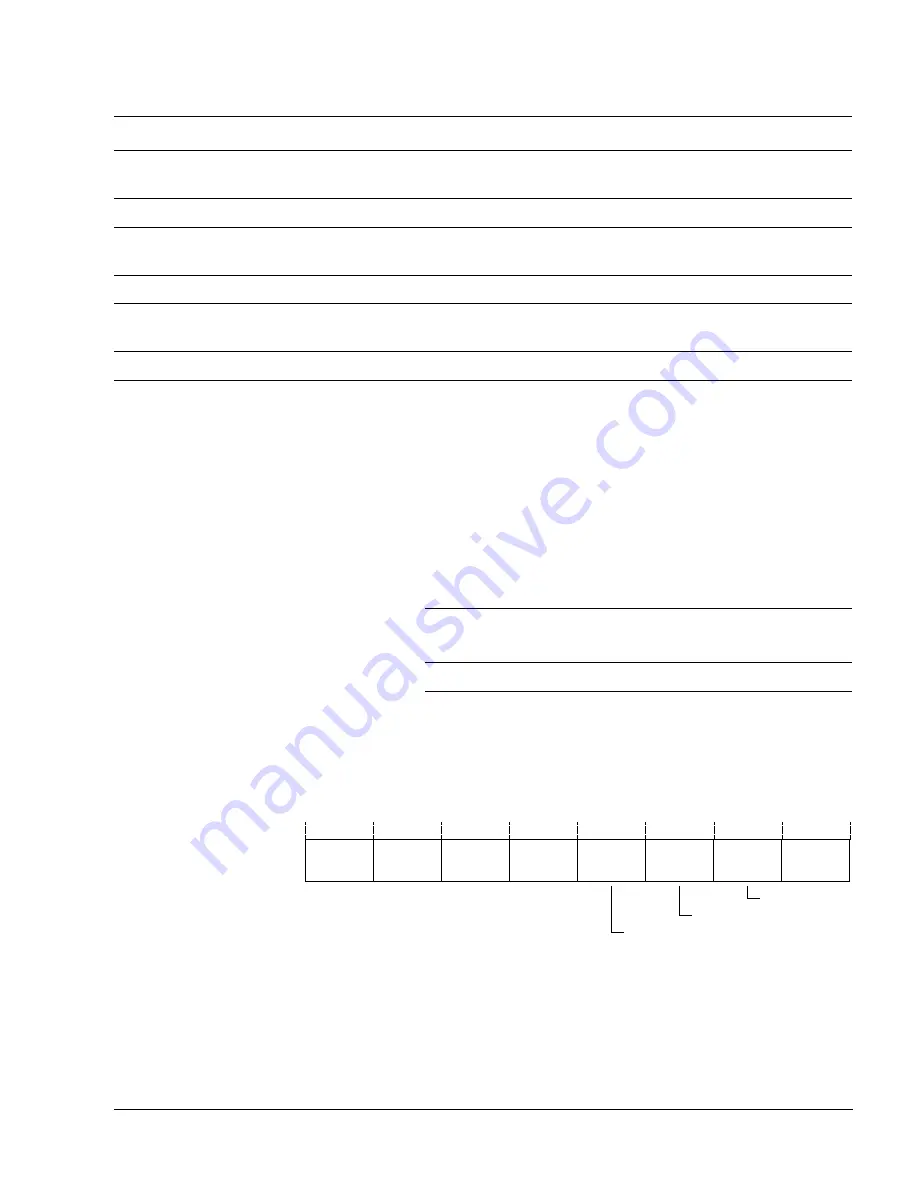

Figure 11-6

shows the DBGDEVID bit assignments.

Figure 11-6 DBGDEVID bit assignments

[19:16]

Version

The Debug architecture version.

0x6

The processor implements ARMv8 Debug architecture.

[15]

DEVID_imp

Reserved, RAO.

[14]

nSUHD_imp

Secure User Halting Debug not implemented bit. The value is:

1

The processor does not implement Secure User Halting Debug.

[13]

PCSR_imp

Reserved, RAZ.

[12]

SE

EL3 implemented. The value is:

1

The processor implements EL3.

[11:0]

-

Reserved,

RES

0.

Table 11-8 DBGDIDR bit assignments (continued)

Bits

Name

Function

EL0

(NS)

EL0

(S)

EL1

(NS)

EL1

(S)

EL2

EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

-

RO

RO

RO

RO

RO

CIDMask

31

4 3

0

PCsample

28 27

24 23

20 19

16 15

12 11

8 7

AuxRegs

DoubleLock

VirtExtns

VectorCatch

BPAddrMask

WPAddrMask