Embedded Trace Macrocell

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

13-31

ID021414

Non-Confidential

The TRCEXTINSELR can be accessed through the internal memory-mapped interface and the

external debug interface, offset

0x120

.

13.8.20 Counter Reload Value Registers 0-1

The TRCCNTRLDVRn characteristics are:

Purpose

Defines the reload value for the counter.

Usage constraints

Accepts writes only when the trace unit is disabled.

Configurations

Available in all configurations.

Attributes

See the register summary in

Table 13-3 on page 13-10

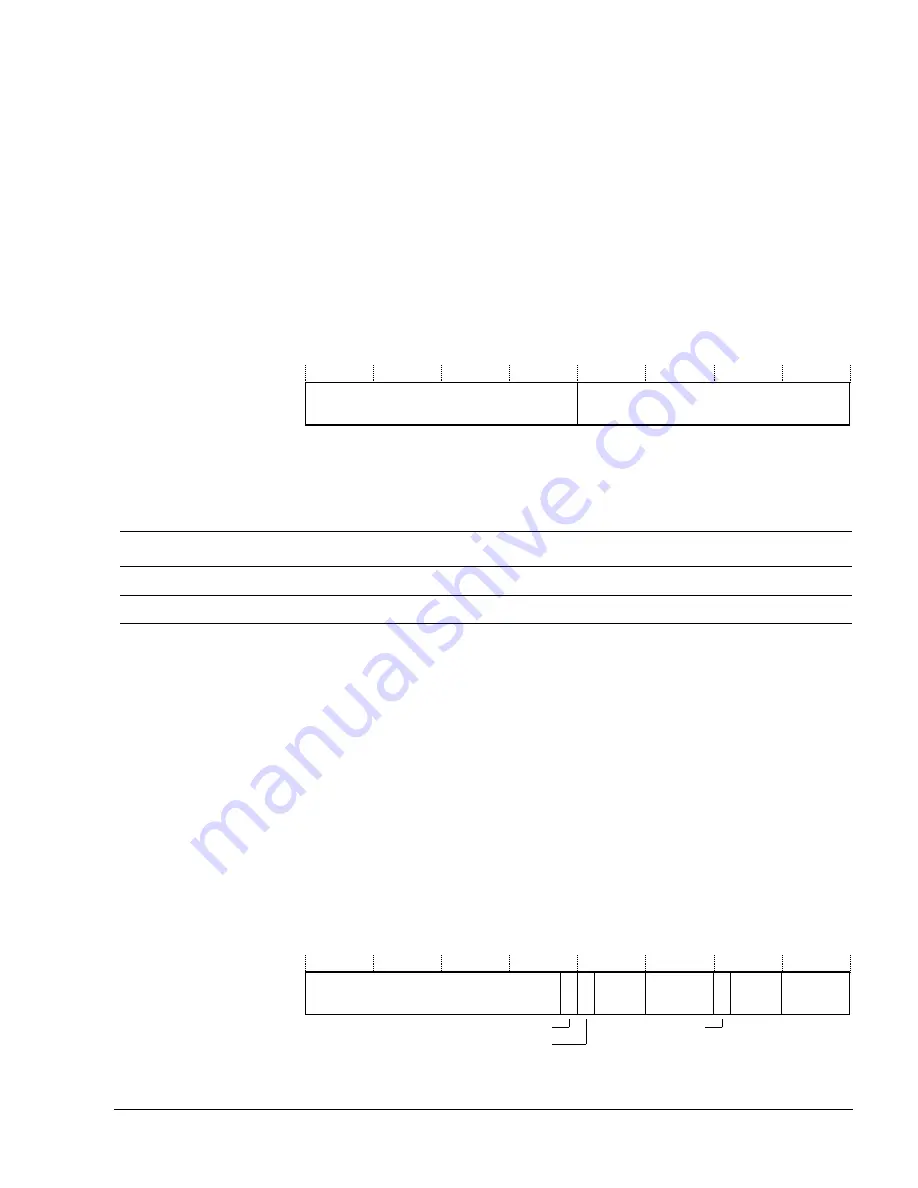

Figure 13-22

shows the TRCCNTRLDVRn bit assignments.

Figure 13-22 TRCCNTRLDVRn bit assignments

Table 13-23

shows the TRCCNTRLDVRn bit assignments.

The TRCCNTRLDVRn registers can be accessed through the internal memory-mapped

interface and the external debug interface, offsets:

TRCCNTRLDVR0

0x140

.

TRCCNTRLDVR1

0x144

.

13.8.21 Counter Control Register 0

The TRCCNTCTLR0 characteristics are:

Purpose

Controls the counter.

Usage constraints

Accepts writes only when the trace unit is disabled.

Configurations

Available in all configurations.

Attributes

See the register summary in

Table 13-3 on page 13-10

.

Figure 13-23

shows the TRCCNTCTLR0 bit assignments.

Figure 13-23 TRCCNTCTLR0 bit assignments

31

16 15

0

RES

0

VALUE

Table 13-23 TRCCNTRLDVRn bit assignments

Bits

Value

Function

[31:16]

-

Reserved,

RES

0.

[15:0]

VALUE

Defines the reload value for the counter. This value is loaded into the counter each time the reload event occurs.

RES

0

RES

0

RES

0

31

16 15 14

12 11

8 7 6

4 3

0

RLDSEL

CNTSEL

RLDSELF

CNTTYPE

17

RLDTYPE