Debug

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

11-42

ID021414

Non-Confidential

11.11.3 ROM table register descriptions

This section describes the ROM table registers.

Table 11-28 on page 11-41

provides

cross-references to individual registers.

ROM entry registers

The characteristics of the ROMENTRY

n

are:

Purpose

Indicates to a debugger whether the debug component is present in the

processor's debug logic. There are 16 ROMENTRY registers in the

Cortex-A53 processor.

Usage constraints

These registers are accessible as follows:

Table 11-1 on page 11-5

describes the condition codes.

Configurations

There is one copy of this register that is used in both Secure and

Non-secure states.

Attributes

See the register summary in

Table 11-28 on page 11-41

.

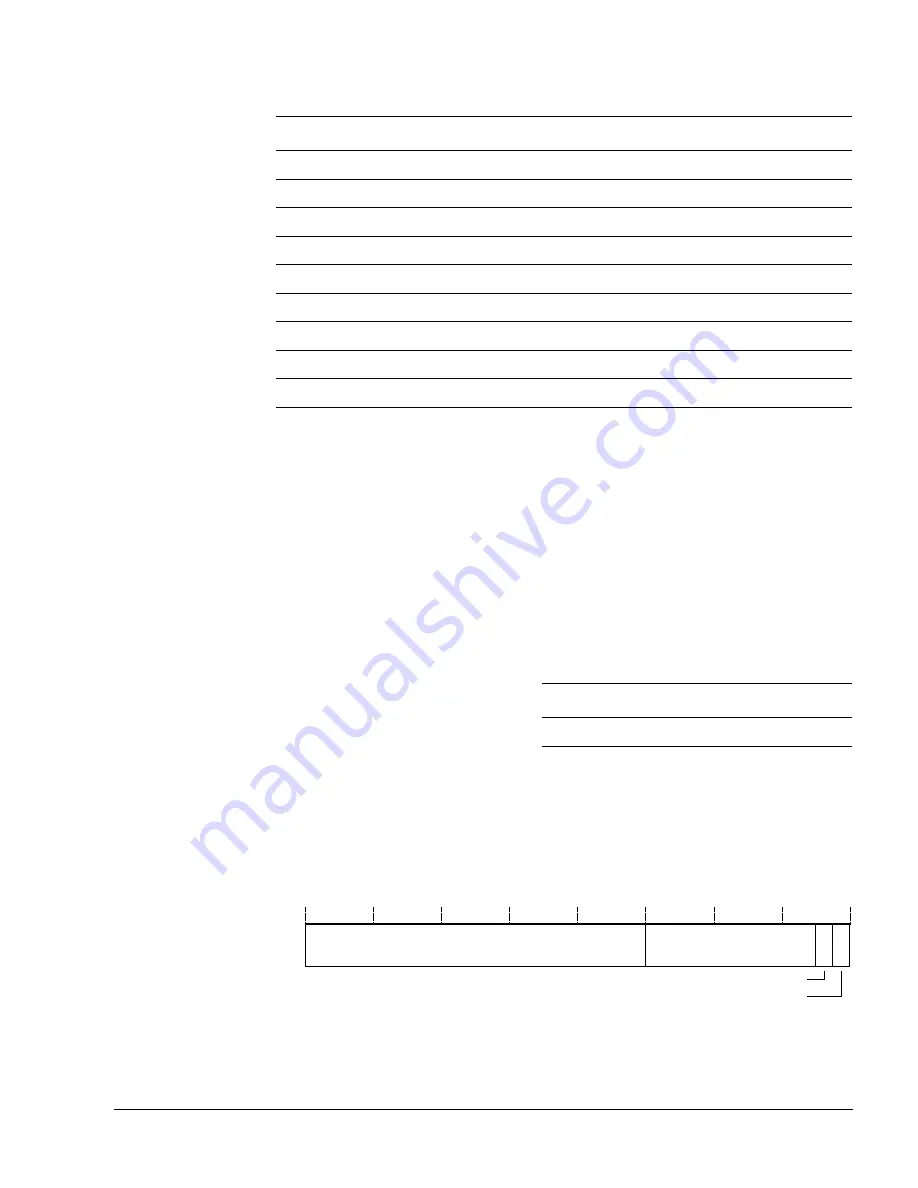

Figure 11-21

shows the bit assignments for a ROMENTRY register.

Figure 11-21 ROMENTRY bit assignments

0xFDC

ROMPIDR7

RO

Peripheral Identification Register 5-7

on page 11-49

0xFE0

ROMPIDR0

RO

Peripheral Identification Register 0

on page 11-45

0xFE4

ROMPIDR1

RO

Peripheral Identification Register 1

on page 11-46

0xFE8

ROMPIDR2

RO

Peripheral Identification Register 2

on page 11-47

0xFEC

ROMPIDR3

RO

Peripheral Identification Register 3

on page 11-47

0xFF0

ROMCIDR0

RO

Component Identification Register 0

on page 11-49

0xFF4

ROMCIDR1

RO

Component Identification Register 1

on page 11-50

0xFF8

ROMCIDR2

RO

Component Identification Register 2

on page 11-51

0xFFC

ROMCIDR3

RO

Component Identification Register 3

on page 11-51

Table 11-28 ROM table registers (continued)

Offset

Name

Type

Description

Off DLK

OSLK

EDAD

SLK

Default

-

-

-

-

-

RO

31

0

RES

0

Format

1

2

11

Component present

Address offset

12