System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-147

ID021414

Non-Confidential

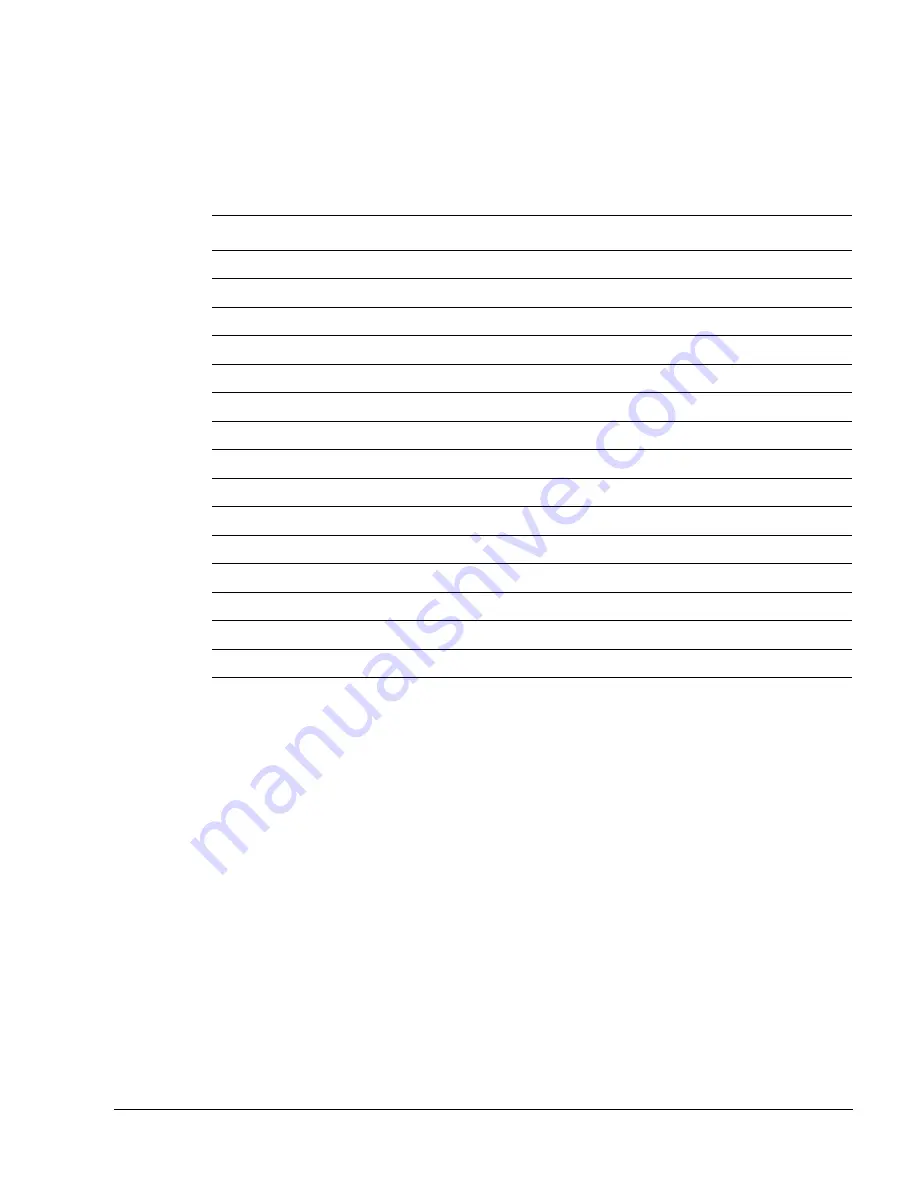

4.4.16

64-bit registers

Table 4-136

shows the 64-bit wide CP15 system registers, accessed by the

MCRR

and

MRRC

instructions. See the

ARM

®

Architecture Reference Manual ARMv8, for ARMv8-A architecture

profile

for more information.

Table 4-136 64-bit register summary

Op1

CRm

Name

Reset

Description

0

c2

TTBR0

UNK

Translation Table Base Register 0

1

c2

TTBR1

UNK

Translation Table Base Register 1

4

c2

HTTBR

UNK

Hyp Translation Table Base Register

6

c2

VTTBR

UNK

Virtualization Translation Table Base Register

0

c7

PAR

UNK

Physical Address Register

on page 4-251

0

c14

CNTPCT

UNK

Physical Timer Count Register

1

c14

CNTVCT

UNK

Virtual Timer Count Register

2

c14

CNTP_CVAL

UNK

Physical Timer CompareValue Register

3

c14

CNTV_CVAL

UNK

Virtual Timer CompareValue Register

4

c14

CNTVOFF

UNK

Virtual Timer Offset Register

6

c14

CNTHP_CVAL

UNK

Physical Timer CompareValue Register

0

c15

CPUACTLR

0x00000000004C8000

CPU Auxiliary Control Register

on page 4-269

1

c15

CPUECTLR

0x0000000000000000

CPU Extended Control Register

on page 4-271

2

c15

CPUMERRSR

-

CPU Memory Error Syndrome Register

on page 4-273

3

c15

L2MERRSR

-

L2 Memory Error Syndrome Register

on page 4-276