System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-235

ID021414

Non-Confidential

MRC p15, 4, <Rt>, c2, c1, 2; Read VTCR into Rt

MCR p15, 4, <Rt>, c2, c1, 2; Write Rt to VTCR

4.5.45

Domain Access Control Register

The DACR characteristics are:

Purpose

Defines the access permission for each of the sixteen memory domains.

Usage constraints

This register is accessible as follows:

Configurations

DACR (NS) is architecturally mapped to AArch64 register

DACR32_EL2. See

Domain Access Control Register

on page 4-92

.

There are separate Secure and Non-secure copies of this register.

DACR has write access to the Secure copy of the register disabled when

the

CP15SDISABLE

signal is asserted HIGH.

DACR has no function when TTBCR.EAE is set to 1, to select the

Long-descriptor translation table format.

Attributes

DACR is a 32-bit register.

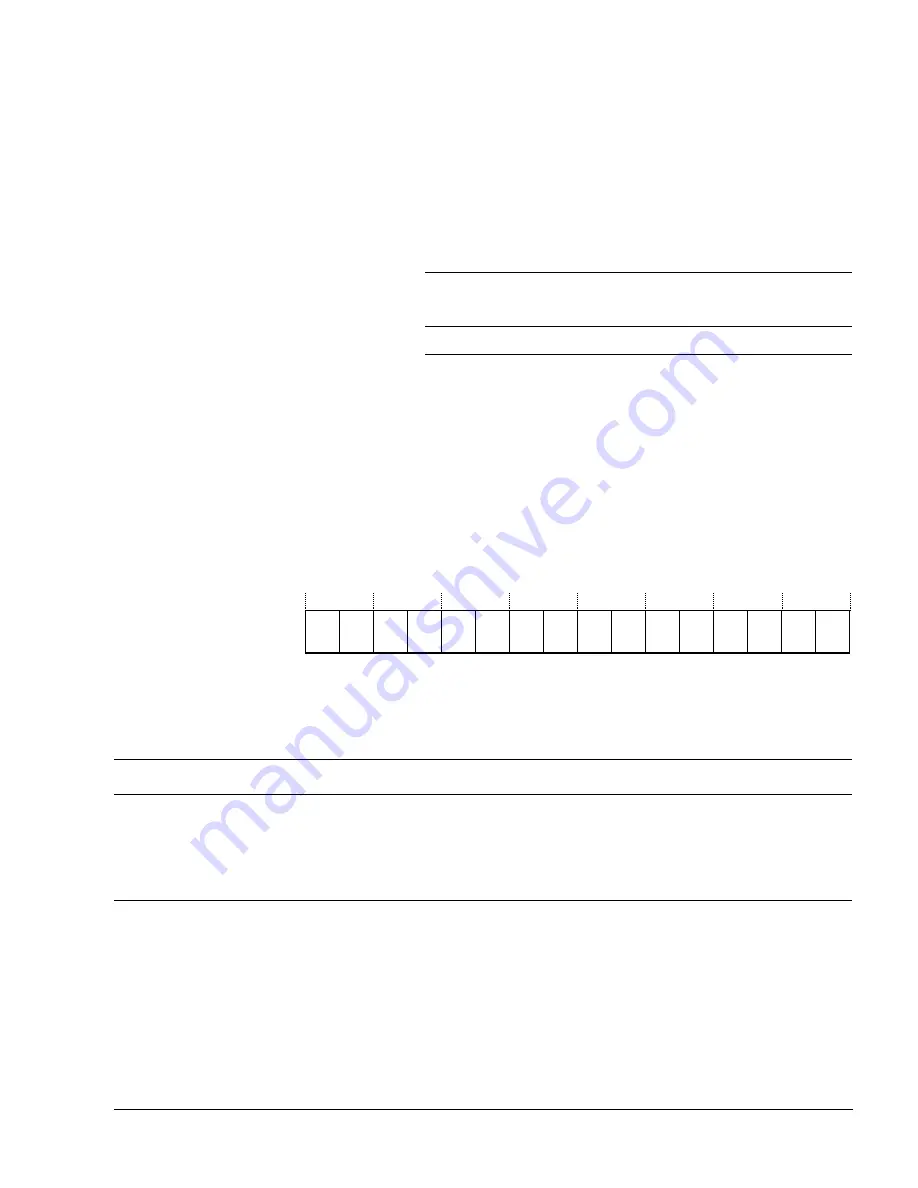

Figure 4-119

shows the DACR bit assignments.

Figure 4-119 DACR bit assignments

Table 4-214

shows the DACR bit assignments.

To access the DACR:

MRC p15, 0, <Rt>, c3, c0, 0 ; Read DACR into Rt

MCR p15, 0, <Rt>, c3, c0, 0 ; Write Rt to DACR

EL0

(NS)

EL0

(S)

EL1

(NS)

EL1

(S)

EL2

EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

-

RW

RW

RW

RW

RW

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Table 4-214 DACR bit assignments

Bits

Name

Function

[31:0]

D<

n

>, bits

[2

n

+1:2

n

], for

n

= 0 to 15

Domain

n

access permission, where

n

= 0 to 15. Permitted values are:

0b00

No access. Any access to the domain generates a Domain fault.

0b01

Client. Accesses are checked against the permission bits in the translation tables.

0b11

Manager. Accesses are not checked against the permission bits in the translation tables.

The value

0b10

is reserved.