Performance Monitor Unit

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

12-18

ID021414

Non-Confidential

The PMCR can be accessed through the internal memory-mapped interface and the external

debug interface, offset

0xE04

.

12.6.2

Performance Monitors Common Event Identification Register 0

The PMCEID0 characteristics are:

Purpose

Defines which common architectural and common microarchitectural

feature events are implemented.

Usage constraints

This register is accessible as follows:

This register is accessible at EL0 when PMUSERENR_EL0.EN is set to 1.

Configurations

The PMCEID0 is architecturally mapped to:

•

The AArch64 register PMCEID0_EL0. See

Performance Monitors

Common Event Identification Register 0

on page 12-9

.

•

The external register PMCEID0_EL0.

There is one copy of this register that is used in both Secure and

Non-secure states.

Attributes

PMCEID0 is a 32-bit register.

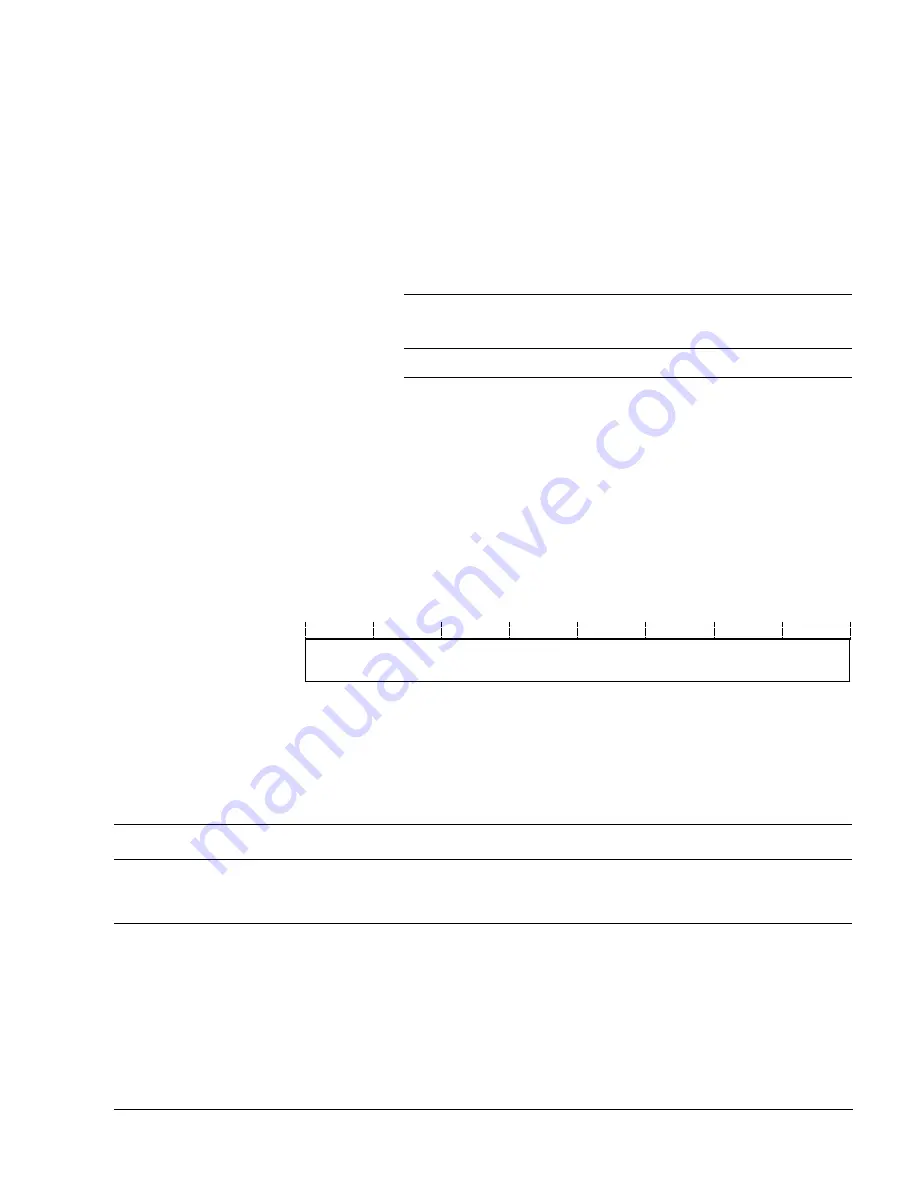

Figure 12-6

shows the PMCEID0 bit assignments.

Figure 12-6 PMCEID0 bit assignments

Table 12-11

shows the PMCEID0 bit assignments with event implemented or not implemented

when the associated bit is set to 1 or 0. See the

ARM

®

Architecture Reference Manual ARMv8,

for ARMv8-A architecture profile

for more information about these events.

EL0

(NS)

EL0

(S)

EL1

(NS)

EL1

(S)

EL2

EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

Config

Config

RO

RO

RO

RO

RO

CE

31

0

8 7

16 15

1

2

3

4

6

11

12

30 29 28 27 26 25 24 23 22 21 20 19 18 17

13

14

9

10

5

Table 12-11 PMCEID0 bit assignments

Bits

Name

Function

[31:0]

CE[31:0]

Common architectural and microarchitectural feature events that can be counted by the PMU event counters.

For each bit described in

Table 12-12 on page 12-19

, the event is implemented if the bit is set to 1, or not

implemented if the bit is set to 0.