System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-40

ID021414

Non-Confidential

MRS <Xt>, ID_AA64DFR0_EL1 ; Read ID_AA64DFR0_EL1 into Xt

Register access is encoded as follows:

4.3.20

AArch64 Instruction Set Attribute Register 0, EL1

The ID_AA64ISAR0_EL1 characteristics are:

Purpose

Provides information about the optional cryptography instructions that the

processor can support.

Note

The optional Cryptography engine is not included in the base product of

the processor. ARM requires licensees to have contractual rights to obtain

the Cortex-A53 Cryptography engine.

Usage constraints

This register is accessible as follows:

Configurations

ID_AA64ISAR0_EL1 is architecturally mapped to external register

ID_AA64ISAR0_EL1.

Attributes

ID_AA64ISAR0_EL1 is a 64-bit register.

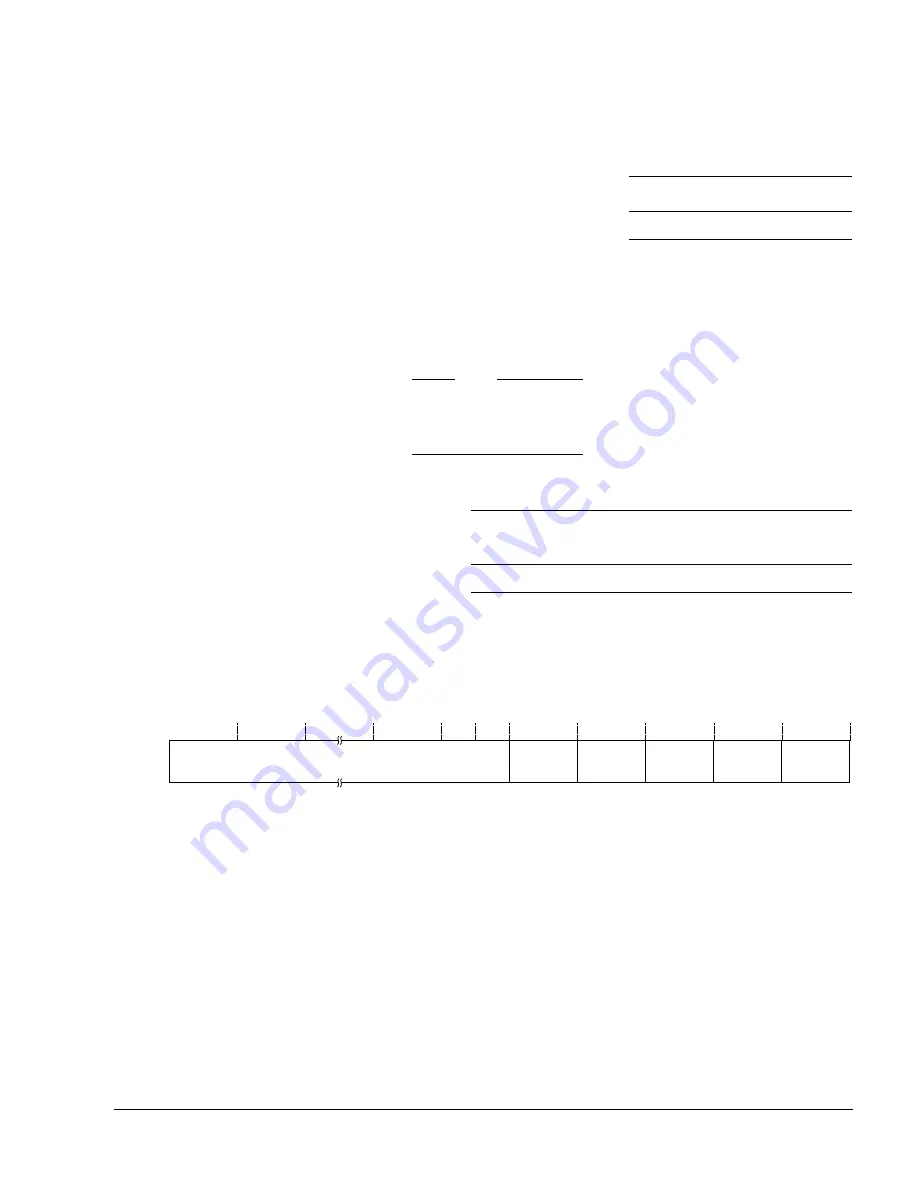

Figure 4-19

shows the ID_AA64ISAR0_EL1 bit assignments.

Figure 4-19 ID_AA64ISAR0_EL1 bit assignments

Table 4-48 ID_AA64DFR0_EL1 access encoding

op0

op1

CRn

CRm

op2

11

000

0000

0101

000

EL0

EL1

(NS)

EL1

(S)

EL2

EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

RO

RO

RO

RO

RO

63

0

RES

0

RES

0

AES

SHA1

SHA2

16 15

12 11

8 7

4 3

CRC32

20 19