Debug

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

11-8

ID021414

Non-Confidential

11.4

AArch64 debug register descriptions

This section describes the debug registers in the AArch64 Execution state. The

AArch64 debug

register summary

on page 11-6

provides cross-references to the individual registers.

11.4.1

Debug Breakpoint Control Registers, EL1

The DBGBCR

n

_EL1characteristics are:

Purpose

Holds control information for a breakpoint. Each DBGBVR_EL1 is

associated with a DBGBCR_EL1 to form a

Breakpoint Register Pair

(BRP). DBGBVR

n

_EL1 is associated with DBGBCR

n

_EL1 to form

BRP

n

.

Note

The

range

of

n

for DBGBCR

n

_EL1 is 0 to 5.

Usage constraints

These registers are accessible as follows:

Configurations

DBGBCR

n

_EL1 are architecturally mapped to:

•

The AArch32 DBGBCR

n

registers.

•

The external DBGBCR

n

_EL1 registers.

Attributes

See the register summary in

Table 11-3 on page 11-6

.

The debug logic reset value of a DBGBCR

n

_EL1 is

UNKNOWN

.

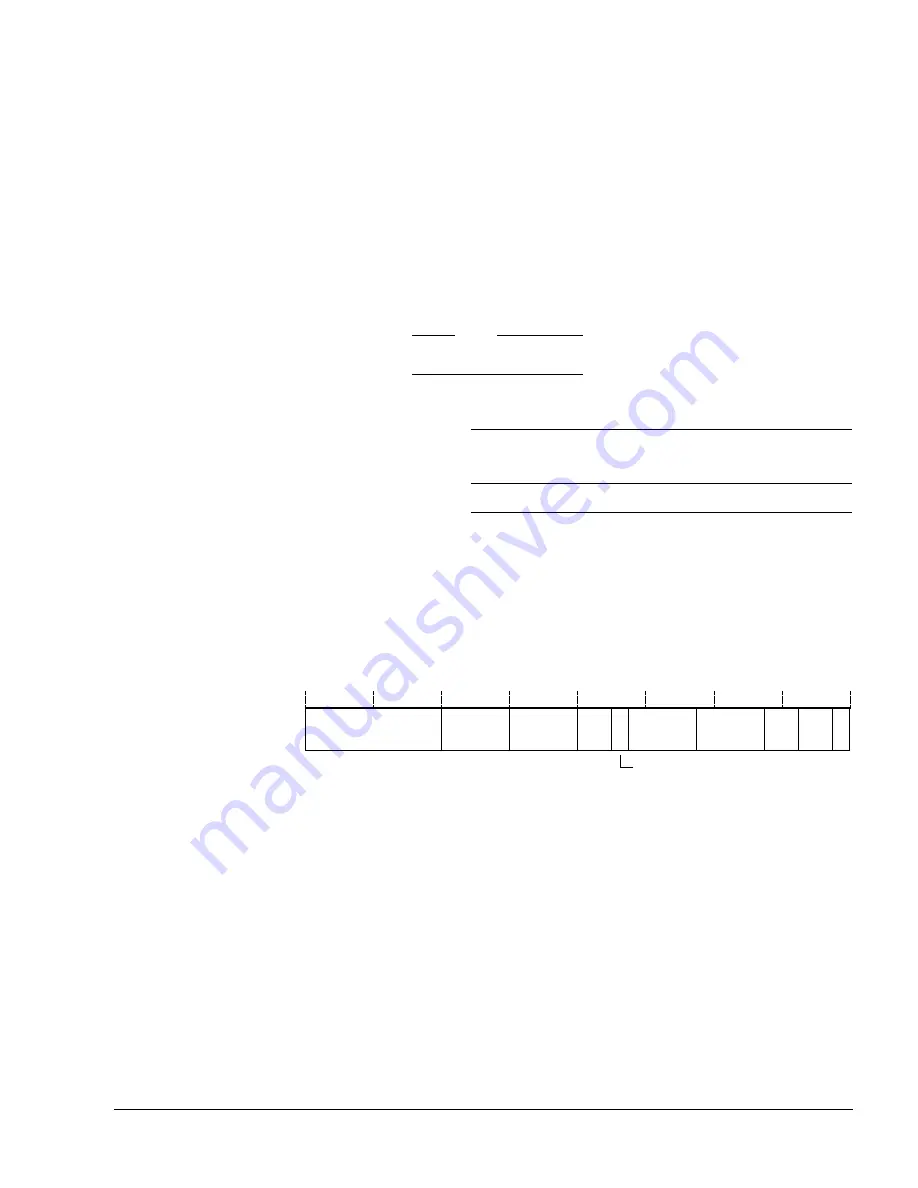

Figure 11-2

shows the DBGBCR

n

_EL1 bit assignments.

Figure 11-2 DBGBCR

n

_EL1 bit assignments

EL0

EL1

(NS)

EL1

(S)

EL2

EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

RW

RW

RW

RW

RW

31

24 23

20 19

16 15

13

9 8

5 4 3 2 1 0

LBN

RES

0

SSC

12

HMC

14

BT

BAS

PMC E

RES

0

RES

0