Rev. 1.10

36

October 23, 2020

Rev. 1.10

37

October 23, 2020

BC66F5652

2.4GHz RF Transceiver A/D Flash MCU

BC66F5652

2.4GHz RF Transceiver A/D Flash MCU

memory read operations are carried out. Clearing this bit to zero will inhibit Flash

memory read operations.

Bit 0

FRD:

Flash Memory read control bit

0: Do not initiate Flash Memory read or indicating that a Flash Memory read process

has completed

1: Initiate a Flash Memory read process

This bit is set by software and cleared to zero by the hardware when the Flash memory

read process has completed.

Note: 1. The FWT, FRDEN and FRD bits cannot be set to “1” at the same time with a single instruction.

2. Ensure that the f

SUB

clock is stable before executing the erase or write operation.

3. Note that the CPU will be stopped when a read, erase or write operation is successfully

activated.

4. Ensure that the read, erase or write operation is totally complete before executing other

operations.

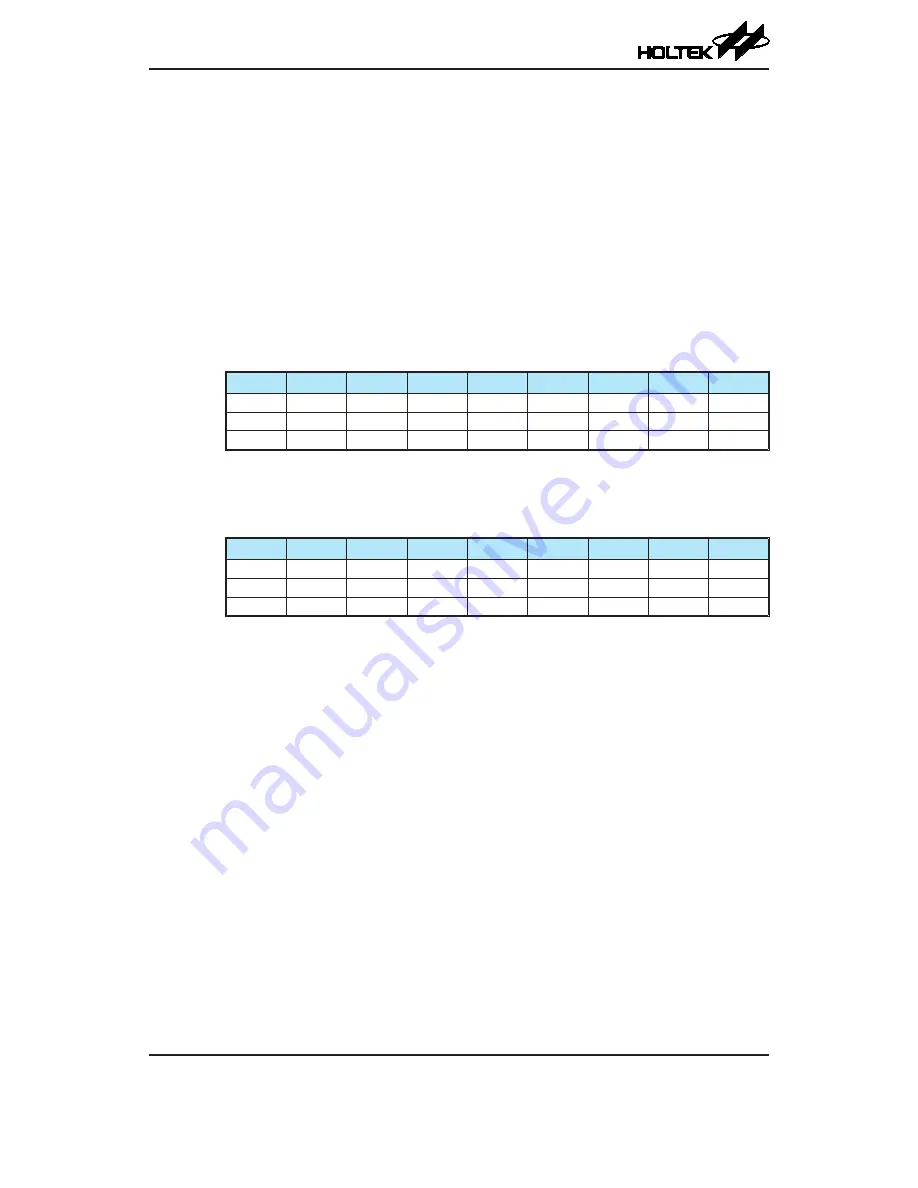

• FC1 Register

Bit

7

6

5

4

3

2

1

0

Name

D7

D6

D5

D4

D3

D2

D1

D0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

POR

0

0

0

0

0

0

0

0

Bit 7~0

D7~D0:

Chip Reset Pattern

When a specific value of “55H” is written into this register, a reset signal will be

generated to reset the whole chip.

• FC2 Register

Bit

7

6

5

4

3

2

1

0

Name

—

—

—

—

—

—

FWERTS

CLWB

R/W

—

—

—

—

—

—

R/W

R/W

POR

—

—

—

—

—

—

0

0

Bit 7~2

Unimplemented, read as “0”

Bit 1

FWERTS

: Erase time and Write time selection

0: Erase time is 3.2ms (t

FER

) / Write time is 2.2ms (t

FWR

)

1: Erase time is 3.7ms (t

FER

) / Write time is 3.0ms (t

FWR

)

Bit 0

CLWB:

Flash Memory Write buffer clear control

0: Do not initiate a Write Buffer Clear process or indicating that a Write Buffer Clear

process has completed

1: Initiate a Write Buffer Clear process

This bit is set by software and cleared to zero by hardware when the Write Buffer

Clear process has completed.

Flash Memory Erase/Write Flow

It is important to understand the Flash memory Erase/Write flow before the Flash memory contents

are updated. Users can refer to the corresponding operation procedures when developing their IAP

program to ensure that the flash memory contents are correctly updated.

Flash Memory Erase/Write Flow Descriptions:

1. Activate the “Flash Memory Erase/Write function enable procedure” first. When the Flash

Memory Erase/Write function is successfully enabled, the CFWEN bit in the FC0 register will

automatically be set high by hardware. After this, Erase or Write operations can be executed on the

Flash memory. Refer to the “Flash Memory Erase/Write Function Enable Procedure” for details.

2. Configure the flash memory address to select the desired erase page, tag address and then erase this

page. For a page erase operation, set the FARL and FARH registers to specify the start address of