Rev. 1.10

158

October 23, 2020

Rev. 1.10

159

October 23, 2020

BC66F5652

2.4GHz RF Transceiver A/D Flash MCU

BC66F5652

2.4GHz RF Transceiver A/D Flash MCU

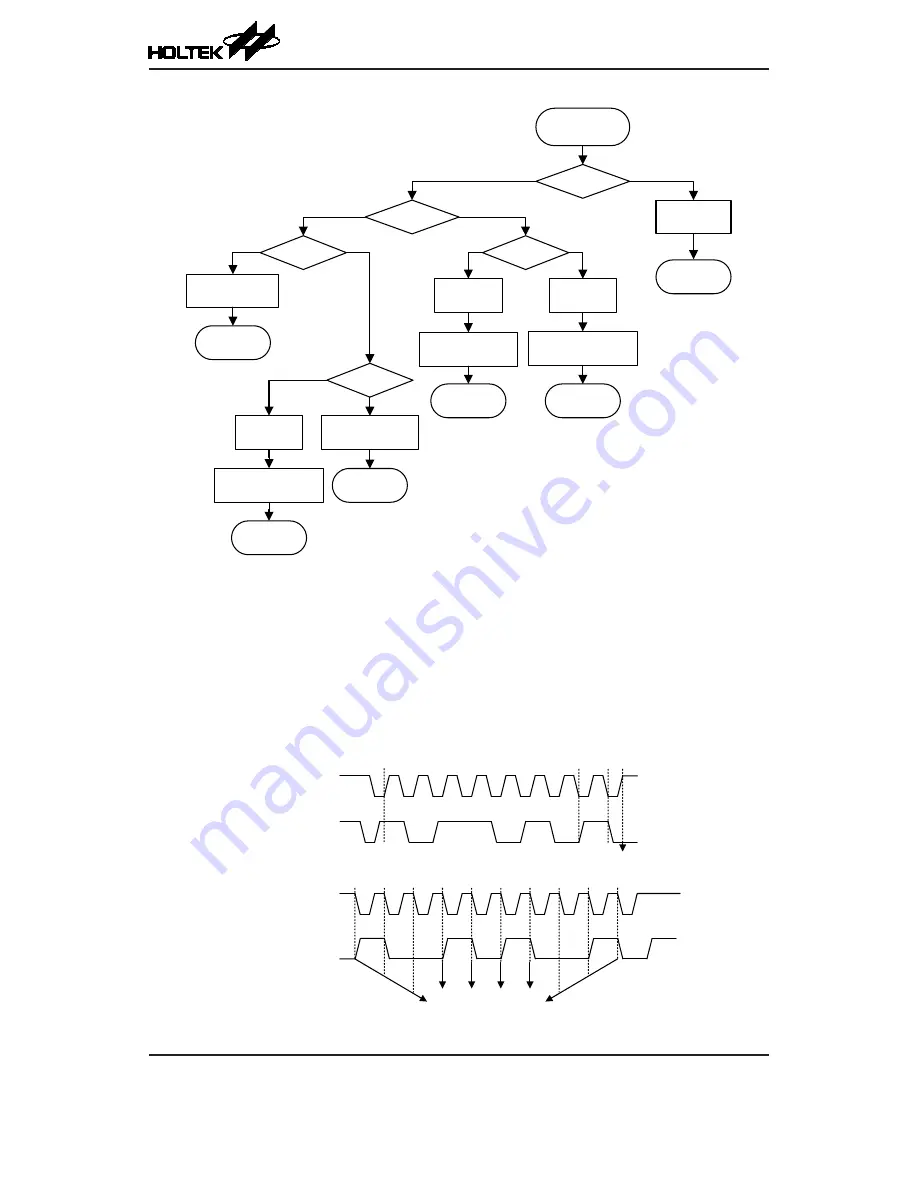

Start

SIMTOF=1?

SET SIMTOEN

CLR SIMTOF

RETI

HAAS=1?

HTX=1?

SRW=1?

Read from SIMD to

release SCL Line

RETI

RXAK=1?

Write data to SIMD to

release SCL Line

CLR HTX

CLR TXAK

Dummy read from SIMD

to release SCL Line

RETI

RETI

SET HTX

Write data to SIMD to

release SCL Line

RETI

CLR HTX

CLR TXAK

Dummy read from SIMD

to release SCL Line

RETI

Yes

No

No

Yes

Yes

No

Yes

No

No

Yes

I

2

C Bus ISR Flow Chart

I

2

C Time-out Control

In order to reduce the I

2

C lockup problem due to reception of erroneous clock sources, a time-out

function is provided. If the clock source connected to the I

2

C bus is not received for a while, then the

I

2

C circuitry and registers will be reset after a certain time-out period. The time-out counter starts

to count on an I

2

C bus “START” & “address match”

condition, and is cleared by an SCL falling

edge. Before the next SCL falling edge arrives, if the time elapsed is greater than the time-out period

specified by the SIMTOC register, then a time-out condition will occur. The time-out function will

stop when an I

2

C “STOP” condition occurs.

Start

SCL

SDA

SCL

SDA

1

0

ACK

Slave Address

SRW

Stop

1

1

0

1

0

1

0

1

0

0

1

0

1

0

0

I

2

C time-out

counter start

I

2

C time-out counter reset

on SCL negative transition

I

2

C Time-out