C

URTISS

-W

RIGHT

P

RODUCT

O

VERVIEW

826448 V

ERSION

5 M

ARCH

2015

P

ROPRIETARY

1-27

Interrupt Routing

Each interrupt line within a source group is routed to a status register, but first passes through

test assertion and enabling logic. If latching is enabled for that bit, the status register latches

the edge of the interrupt pulse and holds the condition until cleared by a write to the status

register. If latching is not enabled, the status register is read-only and not writable. In addition

the test register can be used to force any of the interrupt bits, allowing software to emulate

the assertion of any of the interrupt sources. The enable register bit, if 1, allows the interrupt

to pass through, or else it is blocked.

After the status register, each bit within a source group passes through a mask register that

acts like the enable register. If the mask bit is 1, it allows the interrupt through, or else it is

blocked.

Each interrupt line in the source group is then tied to the source register bits that indicate the

state of the interrupt line at this stage of the routing. See Figure 1.10, "Interrupt Routing Block

(Part A)," on page 1-22 for an illustration of this.

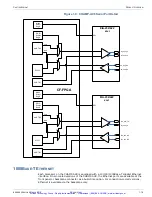

After passing through the source register, all of the bits (up to 32) in the source group are

combined into a single line, such that if any of the bits are asserted, then the single output

line is also asserted. This output line is referred to as GROUP_INTx in Figure 1.13, “Interrupt

Routing Block (Part A),” on page 1-28.

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com