C

URTISS

-W

RIGHT

P

RODUCT

O

VERVIEW

826448 V

ERSION

5 M

ARCH

2015

P

ROPRIETARY

1-5

T

ECHNICAL

D

ESCRIPTION

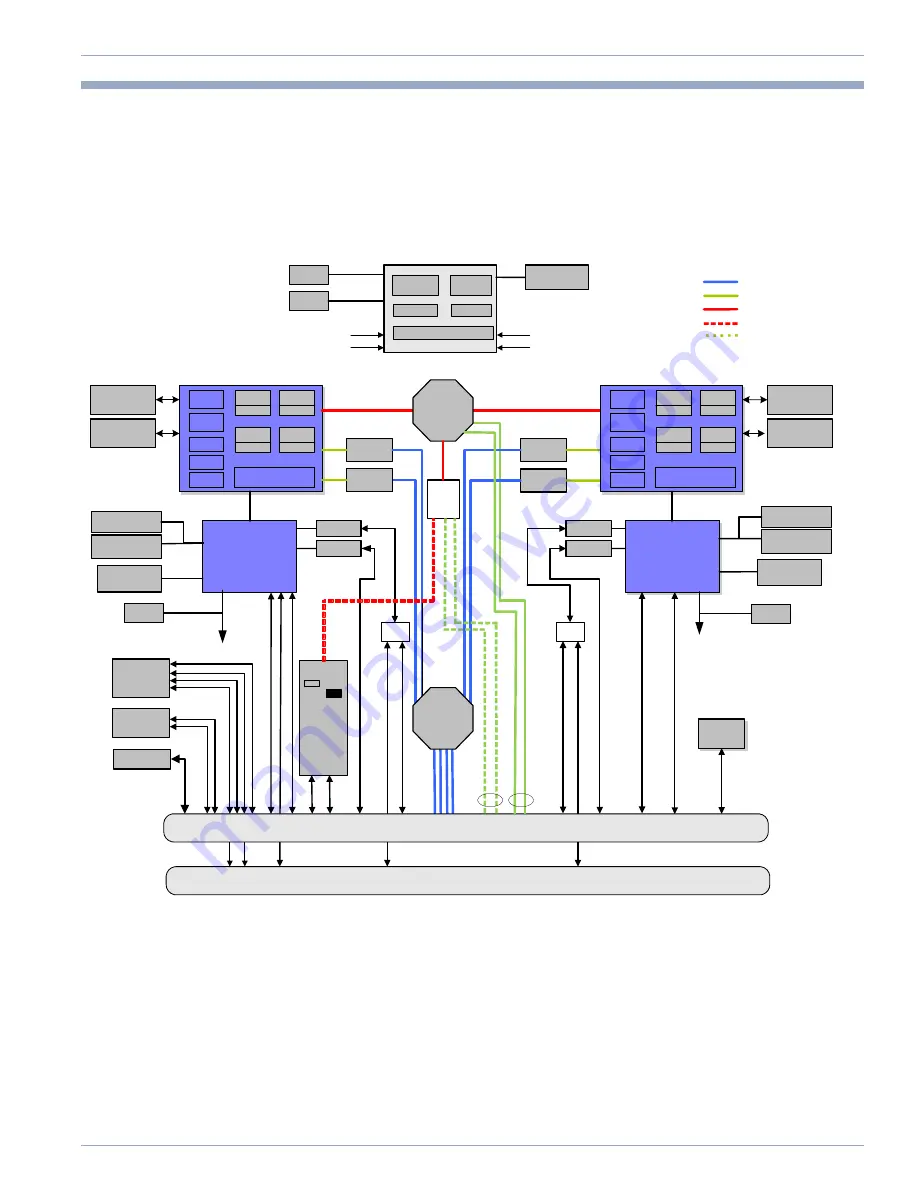

With reference to the high level block diagram illustrated in Figure 1.2 below, the operation of

the CHAMP-AV8 is described in the following sections.

Figure 1.2: CHAMP-AV8 Functional Block Diagram

I/O Hub

I/O Hub

Front Panel

Connector

VPX Backplane

Connector

DDR3 SDRAM

2GB

DDR3 SDRAM

2GB

DDR3 SDRAM

2GB

DDR3 SDRAM

2GB

4 x EIA-232/

2 x EIA-422/

2 x EIA-485

16x GPIO

DMI x4

DMI x4

NAND Flash

8GB

SATA

NAND Flash

8GB

SATA

SPI

LPC

SPI

LPC

LPC_A

TPM

TPM

LPC_B

PCIe/

SRIO

PCIe/

SRIO

Ethernet

Ethernet

Ethernet

Ethernet

Intel Core i7-3612QE or

i7-2715QE quad-core

IPMI

Build Option

PCIe/

SRIO

PCIe/

SRIO

Boot Flash

8 or 16 MB

Recovery Flash

SPI_B

Boot Flash

8 or 16 MB

Recovery Flash

SPI_A

Sync

Clock

Semaphores

Watchdog

Timers

GPIO

Security

NVRAM

256KB

LPC_B

Power

Temp

SPI_B

LPC_A

SPI_A

Node A

SDRAM

Control

SDRAM

Control

L3

PCIe

L1 / L2

Core

L1 / L2

Core

L1 / L2

Core

L1 / L2

Core

PCIe

PCIe

Node A

SDRAM

Control

SDRAM

Control

L3

PCIe

L1 / L2

Core

L1 / L2

Core

L1 / L2

Core

L1 / L2

Core

PCIe

PCIe

32-Lane

x8/

x0

x0/

x8/

2x4

2 x EIA-422/

2 x EIA-485

Build

Option

Build

Option

XMC

J15

J16

Build

Option

PCIe

Gen2

Switch

NT

NT

NT

SRIO

Gen2

Switch

GPIO

16-bits

1000

BaseT_B

USB

_A0

USB

_B0

232/422

Serial

P1

P2

EP[00:07]

1000

BaseBX_B

SATA_B

SATA

_A

422

Serial

1000

BaseBX_A

1000

BaseT_A

USB_A1

1000

BaseT_B

232/422

Serial

1000

BaseT_A

P2

EP[08:15]

P5/

P6

x4 SRIO

x4 PCIe

x8 PCIe

x8 or no PCIe

x4 or no PCIe

Intel Core i7-3612QE or

i7-2715QE quad-core

NT

J14

P4

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com