C

URTISS

-W

RIGHT

P

RODUCT

O

VERVIEW

826448 V

ERSION

5 M

ARCH

2015

P

ROPRIETARY

1-7

PCI E

XPRESS

A

RCHITECTURE

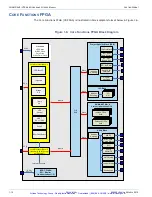

The CHAMP-AV8 makes use of the PCIe interfaces included in the CPU to share and transfer

data between the processors, between cards via the P2 Expansion Plane connectors, and to

communicate with the XMC site, as shown in Figure 1.3 below.

Figure 1.3: CHAMP-AV8 PCI Express Distribution

Each processor connects with an on-board PCIe switch via an 8-lane Gen2 PCIe interface. The

PCIe switch features non-transparent ports allowing each processor a full memory map, and

access to the memory of the other processor. The CHAMP-AV8 presents two PCIe ports to the

P2 expansion plane connector to form connections to I/O devices and/or other cards enabled

with PCIe on P2 (such as the CHAMP-AV8). See Table 1.1, “XMC/Expansion Plane Interface

Build-Time Options for PCIe,” on page 1-8 for details. PCIe switch ports connected to P2

and/or the XMC site may be configured to enable or disable non-transparency, and may

therefore be used with endpoints or root complexes.

I/O Hub

PCIe

Switch

SDRAM

Control

SDRAM

Control

L3

PCIe

PCIe

PCIe

32- Lane

NT

NT

Build

Option

NT, DMA

NT, DMA

XMC

Pn4 J6

x8

Port 16, 20

Port 4

Node A

L1 / L2

Core

Core

Core

L1 L2

/

Core

L1 L2

/

L1 L2

/

Node A

SDRAM

Control

SDRAM

Control

L3

PCIe

L1 / L2

Core

Core

Core

PCIe

PCIe

L1 L2

/

Core

L1 L2

/

L1 L2

/

x8

x8

Port 0,2

Port 8,12

DMI x4

DMI x4

P2

EP[08:15]

P2

EP[00:07]

Intel Core i7 quad-core

Intel Core i7 quad-core

x4

Port 6

x4

x8/x0

I/O Hub

x0

2 x4 /

1 x8

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com