CHAMP-AV8 (VPX6-462) H

ARDWARE

U

SER

’

S

M

ANUAL

C

URTISS

-W

RIGHT

A-28

P

ROPRIETARY

826448 V

ERSION

5 M

ARCH

2015

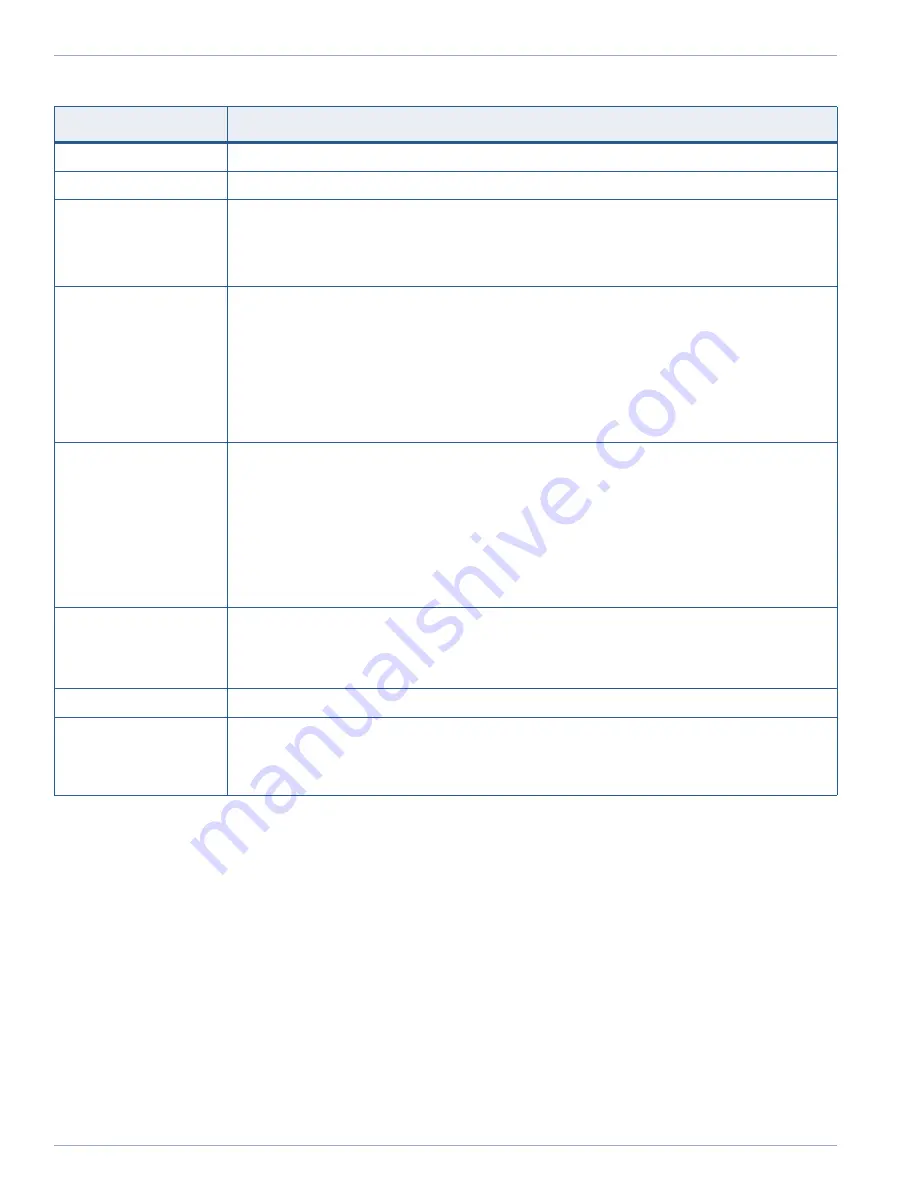

CHAMP-AV8 Signal

Description

CF_SOFT_JMP_L[1:0]

Software Jumpers

CF_WD_DIS_L

Watchdog Disable - Disables watchdog reset (Active low).

RS422_A2_TX_P/N

RS422_A2_RX_P/N

RS422_B2_TX_P/N

RS422_B2_RX_P/N

RS-422/485 or RS232 Ports 3 and 4. NOTE: RS422_TX3_P may be used as RS232_TX3,

RS422_RX3_P may be used as RS232_RX3, RS422_TX4_P may be used as RS232_TX4,

RS422_RX4_P may be used as RS232_RX4.

RS232_A0_TX

RS232_A1_TX

RS232_B0_TX

RS232_B1_TX

RS232_A0_RX

RS232_A1_RX

RS232_B0_RX

RS232_B1_RX

Four base card RS232 (EIA-232) Ports.

ETHA_TRX[0]_P/N

ETHA_TRX[1]_P/N

ETHA_TRX[2]_P/N

ETHA_TRX[3]_P/N

ETHB_TRX[0]_P/N

ETHB_TRX[1]_P/N

ETHB_TRX[2]_P/N

ETHB_TRX[3]_P/N

1000Base-T, Nodes A and B: GigE signals selected via build option between front panel J1 connector

and backplane P4 connector. GigE signals are not present on these pins when configured for front

panel connection. Mapped in accordance with VITA 65 specification.

UTPA_TX_P/N

UTPA_RX_P/N

UTPB_TX_P/N

UTPB_RX_P/N

1000Base-BX, Nodes A and B: Signals that are always present on the P4 connector.

Mapped in accordance with VITA 65 specification.

BP_PORT80_EN_L

PORT80 Enable – Reserved for Curtiss-Wright use

BP_PABS_[A/B]_CS0_L

BP_PABS_[A/B]_CLK

BP_PABS_[A/B]_S0

BP_PABS_[A/B]_SI

PABS interface

– Reserved for Curtiss-Wright use

Table A.16:

P4 Basecard I/O Connector Signal Definitions (Continued)

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com